プロセスの微細化を継続するために必要なこと

2025年5月下旬にベルギーで「Setting the stage for AI-driven digital transformation(AIが主導するデジタル変革の基盤を築く)」をメインテーマとして開催された「ITF(imec Technology Forum)World 2025」では、世界中の著名なAI・IoTならびに半導体企業のトップたちが登壇して講演を行った。その中でASMLと並んでオランダを代表する半導体製造装置メーカーであるASMの経営委員会会長兼CEOのヒッチェム・ムサード(Hichem M'Saad氏が「Every monolayer matters(すべての単原子層が重要)」と題した講演を行った。

同氏は、「半導体業界は、人工知能(AI)、高性能コンピューティング(HPC)、データストレージ、6G、自動運転、電気自動車(EV)への需要の急増に牽引され、2020年代末までに市場規模1兆ドルに達する軌道に乗っている。この成長は、コンピューティング技術とストレージ技術の確立されたロードマップによって支えられており、ロジックデバイスとメモリデバイスの垂直3Dアーキテクチャへの移行、そして新しい材料と極薄の成膜技術によって実現される継続的なスケーリング(比例縮小)に依存している」と新材料と成膜技術の重要性を強調した。

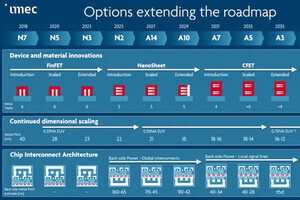

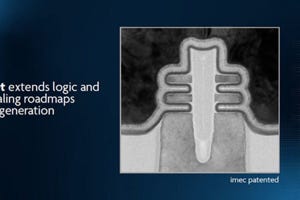

ロジックデバイスは微細化に伴い、2012年以降で採用されてきた技術ノード(22nm〜5/3nm)ではトランジスタ構造が従来のプレーナー構造からFinFET構造に替わり、チャネルやソース・ドレインがシリコン基板上にせりあがる3D構造になった。3/2nm〜1nmではチャネルをゲートがとり囲んだGAA(Gate-All-Around)構造が採用されるほか、2030年代に実用化されるであろう0.7nm以降のプロセスではCFET(Complimentary FET:相補型電界効果トランジスタ)が採用される見込みである。

DRAMでは、技術ノードが16nm〜9nmでは6F2メモリセル配置が採用されるが、その後はセル面積が66%縮小した4F2配置がしばらくの間採用される見込みである。また、2030年代に入ると、DRAMもNAND同様に3次元化することが予想され、2031年には128層の3D DRAMが登場し、2034年には220層へと積層が進む見込みである。

N7(いわゆる7nmプロセス)程度までは過去50年にわたる配線ピッチのスケーリングを中心に微細化が進められてきたが、N3(いわゆる3nmプロセス)以降は、S/DTCO (システム・デバイス設計・プロセス技術同時最適化)と新材料の採用なしでは性能に見合った微細化が難しくなっており、今後のさらなる微細化には、原子レベルのプロセス制御が必要になるとする。

次世代プロセスで重要になるALDとエピ成長

「原子層堆積(ALD)とエピタキシャル成長(エピ成長)プロセスは、これから先の最先端技術ノードにおいて極めて重要な役割を果たす」とムサード氏は強調する。

ALDは原子を一層ずつ堆積させるため、あらゆる単原子層が半導体デバイスの全体的な性能と信頼性に貢献する。同様に、エピ成長は基板上に単結晶層を堆積する。これにより、デバイス性能を向上させ、さらなる微細化を可能にする新材料の統合が可能になる。

テクノロジーが複雑化・微細化していくにつれ、個々のモノレイヤーがデバイス全体の構造、性能、そして信頼性に大きく貢献するようになる。そのため、ALDプロセスとエピプロセスによるモノレイヤーレベルの制御と精度は不可欠となる。

実際、微細化が進み、新材料を用いた堆積層が増加するにつれて、ALD工程は増加の一途である。例えば、Siナノシートを用いたGAA構造において、チャネルを取り巻くゲート絶縁膜(IL+HfO2)のサブÅレベルのばらつきがトランジスタのしきい値電圧の変動をもたらす。このため、ALDによる精密膜厚制御が必要になる。

また、エピ成長におけるオングストローム・レベルのチャネル厚制御の実例として、GAAやCFETにおいては、SiGe層とSi層 を相互にエピ成長させ、その後、犠牲層であるSiGe層のみエッチングで除去してSi単結晶のチャネルが宙に浮く構造を形成することになるが、サブモノレイヤーの厚み制御とSi/Geの組成比の精密制御が必須となるとし、そのためにはエピ成長時に、300mmウェハ全面にわたり、温度変動を正確に±0.1℃に制御する必要があるという。

さらに、将来登場する3D DRAMにおいては、Siチャネルを100層以上をエピ成長で積層しなければならないが、上から下までチャネル層の厚みがばらつかぬように制御する必要があるとする。

加えてCFETの先には、従来のSiに代えてMoS2などの遷移金属ダイカルコゲナイド、いわゆる2D(厚みのない2次元)材料をチャネルに採用したFETが登場することが予想されるが、ここでは究極の単原子層制御が要求されるとの見通しを示した。

まとめとして今後の超微細半導体デバイスでは、ロジック、メモリともに、ALDやエピ成長を活用した単原子層精密制御が多用されるようになるであろうとの見通しが示された。