1GHz動作が可能となったAltraのStratix 10 FPGA

Hot Chips 27において、AlteraのプロダクトアーキテクトのMike Hutton氏が、Intelの14nmのTri-Gateプロセス(実質FinFETと同じ)を使うStratix 10 FPGAを発表した。アーキテクチャ的な改善とIntelの14nmプロセスの採用で、現在のStratix Vの2倍の性能となったという。

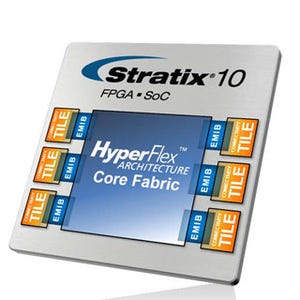

Stratix 10の特徴

Stratix 10は、IntelのEMIB(Embedded Multi-die Interconnect Bridge)という技術を使ってFPGA部と高速トランシーバ部を別のチップとして造っている。これをパッケージ上で接続するので、ロジックとトランシーバを独立に開発して組み合わせることができ、それぞれに最適化した半導体プロセスが使えるというメリットがある。

このような接続には、シリコンインタポーザと呼ぶ配線だけのシリコン基板を使う方法が一般的であるが、全チップを載せる面積の大きなシリコン基板が必要であり、コストが嵩むという問題がある。

そしてStratix 10ではパイプライン構成を柔軟に変更できるHyperFlexと呼ぶ新開発の技術の採用と、Intelの14nmプロセスの採用で1GHz(浮動小数点演算は750MHz)の動作を可能にしている。また、下端にあるSoCブロックにはARM Cortex A-53コアやメモリコントローラがあり、この部分は1.5GHzのクロックで動作する。

マルチチップを接続するEMIB技術

IntelのEMIBは次の図に示すように、微細な配線を持つ基板を、パッケージのチップを接合する部分だけに埋め込んでチップ間の接続を行う技術である。チップ外に出る通常の信号は、はんだボールなどを使って直接パッケージ基板に接続するが、チップ間の接続は微細パターンを持つEMIB基板に接続する。

シリコンインタポーザは全チップを載せる大きなシリコン配線基板が必要であるが、このEMIBはチップを接続する部分だけに小さな基板を埋め込むだけで済み、安価にできるという。ただし、シリコンインタポーザは、その中で自由に配線ができるが、EMIBの場合は、対向する辺の端子間を配線することしかできないと思われる。しかし、これで十分という用途も多いと思われる。

このようにFPGA部と高速トランシーバ部のチップを分離して作ることにより、アナログ部を持つ高速トランシーバの設計をデジタルのロジック部の設計と切り離すことができるので、性能を向上させ、歩留まりも向上させられる。

前の図では高速トランシーバ部は6個のチップで構成されており、すべて同じチップではなく異なるトランシーバチップを搭載することもできるし、この図のように4個搭載という派生品を作ることもできる。

さらに高速トランシーバチップはそのままで、新規のFPGA部と組み合わせたりすることも可能で、開発の自由度が高まる。

|

|

FPGA部と高速トランシーバ部のチップを分けることにより、トランシーバのアナログ部をディジタルのFPGAのロジック部から分離でき、性能や歩留まりを改善できる。また、両者の組み合わせを変えた派生製品が作りやすい |

(次回は9月16日に掲載します)