3次元実装でトランジスタ数の増加速度の維持を目論むTSMC

「次の大きなフロンティア:チップレットとその先」と題して講演したTSMCの研究開発担当VPのDoug Yu氏は、チップレットに続いて、2.5~3D実装によりムーアの法則を継続させ、さらに発展させる手法も紹介した。

ICに搭載されるトランジスタ数は1964年以来2年に2倍のペースで増加してきたが、実は最近、このペースを上回るペースで半導体デバイスのトランジスタ数が増えている。

-

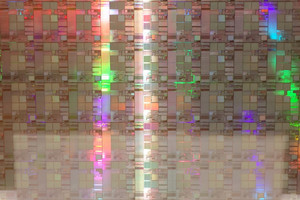

ムーアの法則に沿ったICに搭載されるトランジスタ数の増加。従来のようにSoCの縮小を示す「ムーアの法則1.0」、新たに登場したSoP(System on Package)の縮小を示す「ムーアの法則2.0」 (出所:CSTIC発表資料)

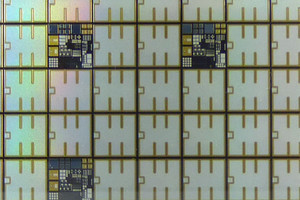

いずれもCoWoS(Chip-on-Wafer-on-Substrate)やINFO(Intergated Fan Out)などの高密度実装技術を用いて複数のチップを1つのパッケージに実装して、搭載トランジスタ数を増加させる技術を採用した手法の登場である。なお、INFOはTSMC用語で、一般にはFOWLP(Fab Out Wafer Level Package)と呼ばれている。この様に、従来どおり複数のチップを2D実装する方式は、インターポーザー(再配線層)を利用した2.5D実装する方式に進化し、さらには3D実装する方式へと進化してきている。2Dから3D実装へ移行することで、相互配線の総延長距離は1/1000に減り、相互配線密度は1000倍増え、チップ間通信速度は100万倍向上するという。

Yu氏は、SoCだけはなくSoP(System on Package)の高密度化のおかげで、ムーアの法則は生き続け半導体産業の成長をもたらすと結論付けた。TSMCは半導体微細化のトップランナーである、という自信に満ちた講演であった。

EUVによる超微細化半導体デバイス量産を目指すASML

ASMLのVPで技術開発センタ長であるAnthony Yen氏(元TSMC)は「EUVリソグラフィの半導体量産導入への道のり」と題した講演を行った。

同氏は、EUVリソグラフィに関する最初の発表は、NTT電子通信研究所が1986年秋の応用物理学会で行った発表であるとし、それから30年余りのEUVリソグラフィの実用化を目指した世界規模での研究開発の紆余曲折した歴史を話した。開発当初は、NTTが「X線縮小投影露光」呼んでおり、技術内容をよく表している言葉だったが、のちに米国勢がEUVリソグラフィと改名した。1990年代、米国においてX線リソグラフィの開発にはすでにDARPAなどから莫大な補助金が出ており、いまさらX線の名前の入った研究には補助金が支給されにくいため、新たな補助金取得に有利なように斬新な「EUV」と改名したという。つまり、米政府から補助金を獲得するための命名だったわけである。

EUVリソグラフィは30年余りに渡り実用化を目指して世界中の企業や研究機関、そして産官学コンソーシアムや国家プロジェクトで研究されてきた。

日本でも、NTTに続き、日立製作所、ニコン、キヤノンなどの企業が研究を行ってきたが、道半ばで研究や装置開発から撤退していった。一方、Selete-EUVL、EUVA、Mirai、Selete、EIDEC(EUVL Infrastructure Development Center:EUVリソグラフィ基盤開発センター)などのコンソーシアムや国家プロジェクトでも莫大な補助金のもとで研究開発が行われてきた。しかし、これらのコンソーシアムや国家プロジェクトもすで解散してしまった。結局、EUV露光装置を商品化出来たのは、世界で唯一、ASMLのみ(源流はPhilipsの半導体リソグラフィ部門)で、EUV半導体量産に成功したのはTSMCとSamsung Electronicsのみだ。

ASMLは2006年に世界初のフルフィールドEUVリソグラフィ装置(実験機)を出荷し、その後、試作用モデルを経て2017年には量産用モデルを出荷し始めている。一方、最有力ユーザーであるTSMCは、2008年以来、ASMLのEUV露光装置を設置し、微細パターンの露光実験を繰り返してきた。

この間、TSMCは、日米欧の研究コンソーシアムにもメンバーとして加わり情報収集し、ASMLの要求でIntelやSamsungとともに開発共同出資プログラムにも加わり、EUV 実用化一番乗りを目指した。

EUVでどこまで微細化ができるのか?

苦節30数年、ついに2019年にEUVリソグラフィは7nmロジックデバイスの量産生産に導入された。液浸ArFリソグラフィでは4回の多重露光を繰り返さねばならぬのに対してEUVリソグラフィでは1回で済むので、サイクルタイムが短縮され、歩留まりと信頼性が向上したとASMLが2019年12月のIEDMで報告している。

7nmプロセスでは、MOLおよびBEOLの最初の方の工程で合計5~6層にEUVリソグラフィを適用しているが、5nmでは、FEOLの一部、MOL、BEOLの最初の方の工程で10層余に適用され、3nm技術ノードではFEOLからBEOLに至る20層以上に本格的に活用される見込みだとTSMCは考えている。

一方のSamsungは、ロジックに続いて10nmクラスDRAMの第4世代(1a-nm)製品の量産にもEUVリソグラフィを適用することをすでに公表しているため、今後、さらなるEUV露光装置の需要増が期待できる。

また、ASMLは、さらなる微細加工が可能なEUVの次世代機(NA=0.55)の光学系およびハードウェアの基本設計を終えており、プロセスの微細化を今後も継続するめどが立ったとしている。

-

次世代高NA(NA=0.55)のEUVリソグラフィ装置の光学系模式図。左端の光源から出たEUV光は、照明光学系を経て中央上のマスクに集光し、マスクで反射されたパターンは、投影光学系を経て右下の300mmウェハに転写される (原図はASMLの光学系を担当しているCarl Zeiss)

なお、CSTIC2020の基調講演では、このほか、IntelのRavi Mahajan氏から、自社製品の集積度と性能向上を目指したヘテロジニアス3D集積のためのマルチチップパッケジングの紹介があった。かつてIntelは14nmプロセスまでは微細化競争のトップを独走していたが、10nmでプロセス開発がもたつき、長期に渡る製造歩留まり低下に悩まされ、いまだにPC用MPUの供給不足状態が続いているとされる。このため、最近は、ヘテロジニアス3D集積化実装技術によってトランジスタ搭載数増加と性能向上に注力しているように見える。