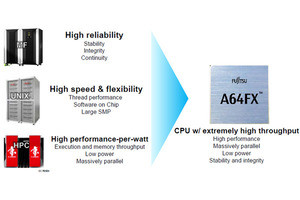

京コンピュータの後継として開発されている通称Post-K(ポスト「京」)コンピュータでは、CPUをSPARCアーキテクチャからArmアーキテクチャに変更した。そしてCPUの名称もA64FXとArmのAが最初に付く名称となった。

今年のCOOL Chipsの大トリの発表となったのが、A64FX CPUについての富士通の山村周史氏の招待講演である。

京コンピュータに使われたSPARC64VIIIfx CPUは45nmプロセスで作られ、8コアでピーク演算性能は128GFlopsであった。FX100スパコンに使われたSPARC64 XIfx CPUは32コア+2アシスタントコアでピーク演算性能は1.1TFlopsに向上している。

ポスト「京」スパコンに使われるA64FX CPUは、先に述べたようにArm V8命令アーキテクチャのプロセサである。これはSPARCのサポートが減ってきていることと、スパコンでもArmアーキテクチャが使われる機運が出てきていることによる。また、Armと共同でScalable Vector Extension(SVE)というベクタ処理命令を新開発し、512bit長のベクタが扱えるようになったことも影響している。

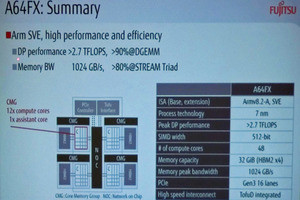

A64FX CPUは、48コア+4アシスタントコアを集積し、演算性能は2.7TFlopsを超える。この性能から行くとクロックは1.76GHz以上ということになる。さらに、ピークFlopsが高いだけではなく、A64FXは、行列積を計算するDGEMMでピークの90%以上の実効性能を持っている。

メモリバンド幅はS64 VIIIfxは64GB/sであったが。GX100では入出力それぞれ240GB/sとなり、A64FXでは1024GB/sとなる。

なお、アシスタントコアは物理的には他のコアと同じものであるが、OSの通信やI/O処理を担当するコアである。このため、計算コアはこれらの処理をする必要がなく、計算に専念できるようになり性能が向上する。またI/Oの割り込みなどで計算時間が変動してしまうOSジッタを小さく抑えることができる。

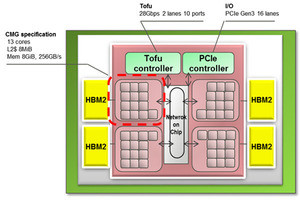

A64FXは12コア+1アシスタントコアとL2キャッシュ、HBM2メモリからなるCMG(Core Memory Group)と呼ぶグループ4組で構成されており、この4つのグループはリングバスで結ばれている。

さらに、多数のノードを接続して大規模スパコンを構成するTofuDネットワークのコントローラと16レーンのPCIe3.0インタフェースがA64FXチップに集積されている。

次の表はA64FXと前世代のCPUの機能の比較で、A64FXの新しいところはArmv8.2A SVE命令アーキテクチャになり、SIMD演算の幅が512bitに拡張されている点である。さらにFirst Fault loadとFP16、INT8/INT16の内積という機能が新設されている。普通のSIMDロードでは、全要素がフォールトを起こしている場合は、要素ごとにフォールトが発生するが、First Fault Loadを使うと、逐次でループを実行する時と同じように、最初の要素のロードだけでフォールトが発生し、その他の要素のロードのフォールトの発生は抑制される。

FP16は16bitの半精度浮動小数点数のサポートで、ディープラーニングなどで効果を発揮する。INT8/INT16の内積は、推論の計算で威力を発揮する

(次回は5月8日に掲載します)