本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

メモリアクセス

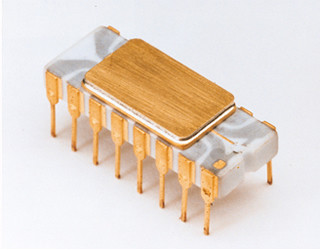

元々のVon Neumann(フォン ノイマン)のストアードプログラムのアーキテクチャでは、メモリ空間は一つであり、命令もデータも同じメモリに格納され、プログラムで命令を書き換えながら実行を行うという機能を含んでいたが、4004では、汎用コンピュータのように、どこか外部からプログラムをメモリに書き込むということは出来ないし、ROMの方がRAMより安く作れるということもあり、命令とデータを分離した構造となっている。

そして、ROMは3サイクルで12ビットのアドレスを受け取り、2サイクルで8ビットの命令を読み出し、一方、RAMはDCL命令でチップを選択した後、8ビットのアドレスを送って、4ビットのデータを読み書きするという動作を行う。

このような構造であるので、ROMは8ビット単位でアドレスが付けられ、RAMは4ビット単位でアドレスが付けられるという非対称な構造となっており、ROMをデータとしてアクセスするために、RAMのデータをアクセスする命令とは異なる命令を必要としている。

一方、最近のプロセサでは、命令とデータは区別するものの、8ビットのバイトを単位としてアドレスが付けられ、命令もデータも同一のメモリアドレス体系(アドレス空間)で対称的にアクセスできるという構造が一般的である。このような単一メモリ空間とする方がアーキテクチャとしては綺麗なのであるが、4ビットデータを単位としてアドレスを付けると、12ビットの命令アドレスでアクセスできる命令数が半減してしまう。

次の図に示すように、4004を用いた最初の製品であるBUSICOM 141-PFの基板には、4004 CPUが1個、4001 ROMが4個(但し、もう1個搭載するスペースがある)、4002 RAMが2個、そして、4003が2個搭載されている。従って、ROMの命令数は1.25K以下であり、最大2K命令のアーキテクチャでも支障はないが、やはり、アクセスできる命令数を半減するのは4004と比較する上で公平ではない気がする。

この問題は、メモリアドレスを12ビットではなく16ビットに拡張すれば解決するが、アドレスを送り出すのに4サイクルを必要とし、全部の命令の実行時間が延びてしまうという問題がある。ということで、あまり美しくないのであるが、MJアーキテクチャでは、命令ROMは8ビット単位、データRAMは4ビット単位のアドレスで、別々の命令でアクセスするという4004の方式を踏襲する。

メモリアクセスのやり方であるが、4004ではDCL命令でアクセスするRAMチップグループを選択し、SRC命令でアクセスする80ビットのグループを選択し、IO命令で目的のアドレスのメモリをアクセスするという回りくどい方式である。電卓をターゲットとしての設計では、このような設計とする必然性があったのかも知れないが、MJアーキテクチャでは、12ビットのメモリアドレスを送れば、ROMは8ビットのデータを読み出し、RAMは4ビットのデータを読み/書きするという単純な構造を想定する。

16ピンパッケージを使うという制約からバス幅は4ビットとすると、1命令で12ビットのアドレスを送出し、4ビットデータを読み書きするためには、RAMをアクセスする命令は4004のような8サイクルの命令処理では無理で、X1サイクルに命令をデコードし、X2~X4サイクルに3分割してメモリアドレスを送り、X5サイクルでデータを転送するという処理が必要である。そしてメモリから読んだデータをアキュムレータに加算するという処理にX6サイクルを必要とするので、メモリをアクセスする命令は11サイクル実行となる。

そのためには、タイミング発生回路は命令に応じて8サイクルと11サイクルのタイミングを発生できるように拡張する必要があるが、これは大して難しいことではない。また、RAM側もこの11サイクル命令に対応して、X2~X4サイクルにアドレスを受け取り、X5サイクルにストア命令の場合はデータを受け取り、ロード命令の場合にはデータを送り出すという機能をサポートするように制御回路を変更する必要があるが、これも若干の回路の追加で可能である。

I/Oアクセス

4004は、SRC命令でアクセス対象となるROMやRAMチップを選択し、その後、IO命令で、選択されたチップ内のポートとデータをやり取りするというアーキテクチャである。

しかし、最近のプロセサでは、メモリマップドIOと言って、メモリ空間にIOポートを配置するアーキテクチャが一般的である。このようにすると特別なIO命令を設ける必要がないし、命令アーキテクチャとしてはIOポートの数にも事実上制限が無くなるというメリットがある。

そこで、MJアーキテクチャでは、このメモリマップドIOの考え方を取り入れ、RAM空間にIOポートを配置し、RAMをアクセスする命令でIOポートをアクセスする方式を採用する。

この方式では、IOポートの分だけRAMの最大容量が減少してしまうが、4002 RAMは4ビット単位で80語のメモリであり、16チップを使ったとしても1280語が最大である。従って、MJアーキテクチャの4K語のRAMアドレス空間の一部をIOポートに流用しても、4004システムに比べて使用できるRAMの語数が減るわけではない。

但し、4004はピン数の制限から、ROM、RAMチップそれぞれにIOポートを内蔵するという構造となっているが、MJアーキでは、IOはRAMと同じアクセス法を使用するので、ROMにはIOポートを内蔵できず、RAM内蔵のIOポートだけで不足する場合は、専用のIOチップが必要になってしまうが、この差異には目をつぶることにして頂きたい。

なぜ、MJアーキテクチャではこのような方針とするのかというと、上記に述べたような理由からこちらの方が上手く行きそうであると思ったと言うしかない。つまり、コンピュータのアーキテクチャ設計は、方程式を解くように誰がやっても正しい答えは一通りというものではなく、建築のアーキテクチャと同様に色々な作り方があり、設計者の考え方が大きく反映されるところが面白いところである。