この記事を読んでいる方が持っているツールがハンマーだけの場合、すべての問題を釘のように扱いたくなるだろう。この難問から抜け出す唯一の方法は、ツールボックスを拡張することである。言い換えると、モバイルチップセットの制約(エネルギー、コスト、温度、電力密度、メモリ容量、速度など)は、HPCやVR システムの制約とは大きく異なるため、より汎用性の高いテクノロジプラットフォームが必要となる。

そのため、我々はシステム、回路、プロセス技術の共同最適化(STCO:System-Technology Co-Optimization、システム・製造協調最適化)によって推進されるまったく新しいパラダイムである「CMOS 2.0」を構想している。

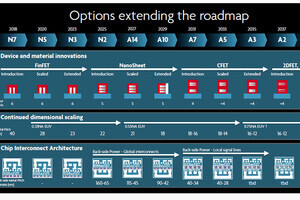

STCOでは、システム設計者がプロセステクノロジーチームと緊密に連携して、既製のスケーリングオプションに頼るのではなく、最も適切なオプションを特定する。テクノロジチームは、次世代製品を開発する際に、特定のシステム仕様も認識する必要がある。アプリケーション、ワークロード、システム制約の多様性には、より幅広いテクノロジ・オプションが必要である。

さまざまなシステムやアプリケーションのニーズに対応できるように、テクノロジプラットフォームを再考する必要がある。CMOS 2.0は、複数の3Dスタックレイヤーでさまざまな機能をスマートに分割して構築されたカスタマイズされたチップを有効に活用ことでこれを実現するものとなる。

ハイブリッドボンディングでメモリ制限に対処し、アクティブインターポーザで帯域幅の制約に対処し、バックサイドの電源供給ネットワークで電力問題を解決する、現在見られる異種システムとは異なり、CMOS 2.0はSoC内に異種性をもたらすという、より革新的なアプローチを採用している。従来のCMOSプラットフォームと同じ「look and feel(外観と使い勝手)」を持ちながら、システム最適化のための柔軟性が高まっている。高密度ロジックレイヤはコストの大部分を占め、依然としてスケーリングが必要である。ただし、他のスケーリングの制約は物理的に他のレイヤに移されることになる。

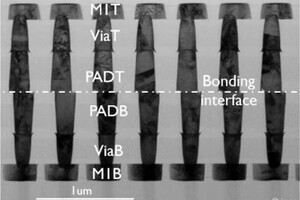

CMOS 2.0は、高密度ピッチCuハイブリッドボンディング、誘電体ボンディング、チップレット統合、ウェハ裏面処理、異種層転送を伴うシーケンシャル3D統合など、既存および新しい高度な2.5Dおよび3D相互接続テクノロジを活用することになる。これにより、SoCの先進的な微細相互接続と、SiPによって提供される先進テクノロジの異種性が実現され、従来のCMOSの制約が実質的に解消される。

CMOS 2.0では、低容量、低駆動トランジスタを使用して短距離相互接続を駆動しつつ、別のレイヤの高駆動トランジスタを使用して長距離相互接続を駆動することができる。また、新たな組み込みメモリは、キャッシュ階層の別のレイヤとして導入できる。さらに、電源の電圧降下の制約なしにスケーリングするための極端なBEOLピッチパターン化も可能になる。汎用CMOSの仕様を満たす必要がなくなるため、2D材料などの非シリコンデバイス、MRAMなどの新しい組み込みメモリ、堆積酸化物半導体の導入なども容易になる。設計者にとって、CMOS 2.0プラットフォームは従来のCMOSのように感じられるが、ツールボックスが大幅に拡張され、より多用途になるというイメージである。

スケーリングはもはやコンピューティングの性能向上を推し進める唯一の答えではないが、CMOS 2.0によってもトランジスタ密度の増加の必要性がなくなるわけではない。ただし、スケーリングの問題は、答えがアプリケーションによって異なるため、より総合的な方法で取り組む必要がある。高密度ロジックはワットあたりのパフォーマンスを最適化し、高駆動ロジックはクリティカルパスの帯域幅とパフォーマンスを維持する。高密度ロジックのような厚膜酸化膜I/O、電源スイッチ、アナログ、MIMCAPなどのスケーリングがうまくいかないデバイスは、よりコスト効率の高いテクノロジノードを使用して別のレイヤに統合できるようになった。不可欠ではあるもののスケーラブルではないすべてのSoCパーツを削除することで、さまざまな新しいタイプのデバイスへの扉も開かれる。

動き始めたCMOS 2.0革命

裏面電力分配ネットワーク技術の実用化は、CMOS 2.0時代に突入したことを示す最初の兆候の1つである。すべての主要ファウンドリは、高性能でエネルギー効率の高い電子デバイスを実現するためにますます重要になっている、ウェハ裏面の電力分配システムを備えた統合チップに移行することを宣言している。ウェハ裏面処理へのアクセスにより、電源スイッチなどのデバイスを統合したり、グローバルクロックルーティングを前面から移行したり、新しいシステム機能を追加したりする機会が生まれている。

おそらく、このパラダイムシフトは、より複雑な技術的な問題をもたらすことが想像される。EDAツールはどのくらいの速さで進化するのか、パーティショニングのコストと複雑さはどの程度なものになるのだろうか、といったものから、CMOS 2.0プラットフォームの熱特性は管理可能だろうかといったものまで幅広いが、それらの問題が解決できているかどうかは、時が経てばわかることとなるだろう。ドイツの哲学者で革命家であるフリードリヒ・エンゲルスの言葉を引用すると「自分が起こそうとしている革命を正確に知る者は誰もいない」ということである。同時に、まさにそれが今の時代を非常に魅力的なものにしていることを意味するものともなる。この未知の領域を進むには、半導体エコシステム全体にわたり緊密な連携をはかり、共同でイノベーションを起こすことが必要である。問題となっているのはムーアの法則そのものではなく、経済成長、科学の進歩、持続可能なイノベーションを可能にするその能力である。

本記事はimecの「The CMOS 2.0 Revolution」を許可を得て翻訳したものとなります

Julien Ryckaert(ジュリアン・リッカート)

Sri Samavedam(スリ・サマヴェダム)