2016年5月にCCIX Consortiumが設立され、2018年6月にはBase Specification 1.0がリリースされたことで普及に弾みも付き、実際今年にはCCIXに対応した製品が出始めるという状況であるが、今年3月にIntelが突如としてCXL Consortiumを設立したことで、Coherent Interconnectの標準化がまた遠のいた印象がある。ちょっとこの辺りを整理してご紹介したいと思う。

Before CCIX

そもそもアクセラレーターなどを接続する際に、Cache CoherencyなInterfaceが欲しい、という要求そのものは、かなり昔から存在した。この場合の「昔」の定義が難しいが、要するにP6以降と考えて頂ければよいかと思う。PCIと、この後継であるPCI ExpressはどちらもI/O Busという性格を前面に打ち出した結果として、あえてProcessor MemoryへのDirect AccessとかCache Coherencyをサポートしなかった。

もちろん独自規格でProcessor Memory Access/Cache Coherencyをサポートするものは一杯あった(そもそもCPUのFSBがこれにあたる)が、標準的な規格ではなかった。最初にこの分野にチャレンジしたのが、HyperTransport Linkである。HyperTransport Linkは元々はCPUとチップセット用のInterconnectであるが、Cache CoherencyなAccelerator用のI/Fという用途は当初から考慮されており、これにむけてAMDはTorrenzaというコード名の取り組みも行っていた。

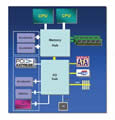

さらには、アクセラレータ用にHTXというコネクタ規格も定義している。このHyperTransport Linkを使ったアクセラレータ、実は筆者も2009年のESC(Embedded System Conference)で見たことがある(Photo01)。図で判る通り、Polluxと呼ばれる入出力コントローラから、HyperTransport Link経由で直接CPU(Opteron)のMemoryに書き込みが可能になっている。ただ、HyperTransport Consortium(やAMD)が予想したほどには、これらは普及しなかった。

-

Photo01:A&DのProcyon System。製品化もなされたが、長くは続かなかった模様。ちなみにProcyonはラックに収める関係か、HTXではなくメザニンコネクタを利用しての接続方式だった

一方のIntelであるが、こちらはもっとストレートに、FSBを利用してAccelerator(主にFPGA)をつなぐ、という技に出た。こちらに紹介しているが、Altera(当時)とXilinxにFSB Licensingを行い、VirtexやStratixを直接CPUのソケットに装着する形で利用可能とした。

確かにFSBを使えばProcessor Memory Direct AccessやCache Coherencyもバッチリである。が、そもそもピン形状(というかパッケージ形状)がまったく異なるから割と無茶である。そこでCPUソケットとFPGAの間に変換基板を挟み、まずCPUソケットに変換基板を装着、その上にFPGAのドーターカードを載せるという、開発中はまだしも本番運用にはどうだろう? と思うようなソリューションを出してきた。

案の定この方式、ほとんど使われなかった。おまけにIntelはその後、FSBをQPIに変更してしまい、そのQPIについてはLicenseを行わなかったから、やっぱりあっという間に過去のものになってしまった。

ただこれではいかんと思ったのだろう。Intelは何とかしてPCI ExpressベースでAcceleratorを接続する方法を模索し始めた。その結果が、GeneseoとExoskeletonである。以前の記事で説明しているが、GeneseoはPCI Expressを利用しながら、オーバーヘッドを最小限とするためのトリックというか、サポートのメカニズム。ExoskeletonはPCI ExpressのATS(Address Translation Services)を利用して、DeviceからProcessor Memoryを直接アクセスできるための仕組みである。

ただ、先の記事を読んでいただくと判るが、GeneseoはともかくExoskeletonは結構大がかりになるというか、ものすごく労力の必要なインプリメントであって、普及は難しいだろうなぁと思ったら案の定まったく実装例が出てこなかった。Geneseoの方はPCI-SIGにゴリ押しして、PCI Express Version 2.1として標準化まで行われたにも関わらず、である。Geneseoだけでは片手落ちで、Exoskeletonまで実装しないとアクセラレータには不十分なのであるが、そのExoskeletonが普及しなければGeneseoが使われる訳もない。かくしてアクセラレータは引き続きPCI Expressベースで利用される事になった。

ただこれもGPU Computingが本格的になってくると、いよいよPCI ExpressのOverhead(というか、Processor Memory Direct Access/Cache Coherencyの欠如によるLatencyの増大)が本格的に問題になってきた。最初に音を上げたのがNVIDIAであり、丁度IBMがPOWER8で外部バスにCAPI(Coherence Attach Processor Interface)と呼ばれるAccelerator用のI/Fを搭載したのと歩調を合わせるように独自のNV-LINKと呼ばれるCache Coherency Busを搭載。NVIDIAのGPU同士の接続だけでなく、POWER8との接続もこのNV-LINK(というか、CAPI)で行えるようにした。

CAPIは2016年にオープン化されたOpenCAPIに進化し、これをサポートするOpenCAPI Consortiumも設立された。ただCAPI/NVLinkが発表された2014年には、まだOpen化の話は一切出ておらず、なので(我が道を行く)IntelとIBM&NVIDIA連合以外のベンダーは、別の方法でProcessor Memory Direct Access/Cache Coherencyを確保したI/Fを用意する必要に迫られた。実はこの取り組みが、特にArmベースのサーバを検討しているベンダーには非常に重要な話であった。

(次回は5月28日の掲載予定です)