FSB Licensing Update

昨年の記事のPhoto76のキャプションで「これが何かがさっぱり判らないのが問題。」と書いた、FPGAを使ったFSB Licensingの話だが、今回は実物がちゃんと展示されていた他、フォローアップセッションも用意されており、だいぶ内容が判ってきた。

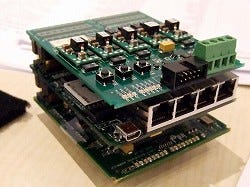

まずは実物(Photo12)である。3層構造になった最上位には受動部品が並び、2層目には4ポートのGbEをカバーするPHYとMACが配され、一番下にはAlteraのStratixシリーズ(おそらくStratix III)が置かれている。で、底面(Photo13)にはPGAのピンが直接埋め込まれている。もう少し判りやすいのは、XilinxのVIRTEX-5を搭載したサンプル(Photo14)で、こちらは底面がむき出しになっていた(Photo15)。要するにこの2種類のボードは、本当にそのままXeon用のSocket 603ないしSocket 604にそのまま装着することを念頭においたボードという訳だ。流石に前回のIDFで、あれがそのままCPUソケットにくっつくとは思わなかったのでちょっと謎であったが、これでやっとあの基調講演の意味が正しく理解できたことになる。ただ物理的にどうやってこれを装着したのかは非常に気になるところ。まさかZIFソケットをロック状態にしておき、真上から力の限り押し込むという訳でもないだろうし、横からドライバなどでロック/アンロックを操作できるスペシャル版のZIFソケットとかを用意するのかもしれない。

|

|

|

Photo12:なんで三層重ね? という疑問もこれで氷解である。基盤面積が限られるから、こうでもしないと収まらなかったということだろう。 |

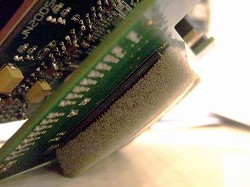

Photo13:こちらはピン曲がり防止用にクッションが貼り付けてあるので、ちょっと判りにくい。 |

|

|

|

Photo14:こちらは「単にVIRTEX-5を搭載してみました」という以上のものではなさそう。内部でロジックを組んですぐ使えます、という例であろう。 |

Photo15:こちらはなぜかクッションなし。これを見て思い出したのが、玄人志向から発売されていたPK-OCK74/EV7。PowerLeapのCPU Upgradesにも近いものがある。 |

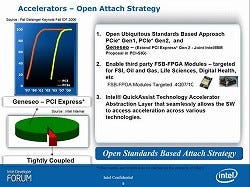

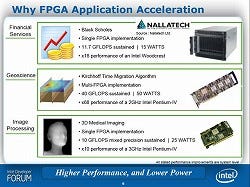

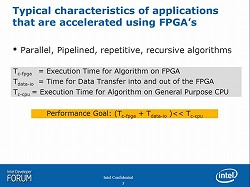

さてそれはともかく、"Intel QuickAssist Technology Enabled FSB-FPGA Application Accelerators"というセッションで、このFSB-FPGAにまつわる話を取り上げていたので、この資料を基に概略を説明したい。最初に登場するのは、先にも出たこのパイチャートであるが(Photo16)、こちらではこのTightly Coupledな部分をどう構築するか、である。ちなみにこのTightly Coupledが必要なアプリケーションとは、Photo17に示すようなCompute-intensiveな用途に向けたものをまずは想定しているようだ。当たり前の話であるが、FPGA内の処理時間とFPGAとの間のデータ転送時間の合計が、CPUのみで処理を行った場合の処理時間よりも相当短くないと、わざわざFPGAを使うメリットが無い事になる(Photo18)。ただTc-fpgaに関しては、これは利用するFPGAとそのインプリメントで決まってくるからどうしようもないとして、Tdata-ioを少しでも短くすることで、なるべく効果的にFPGAを使えるようにしよう、というのがここでの目的となる。

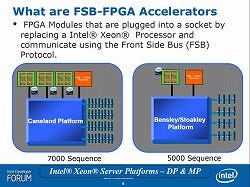

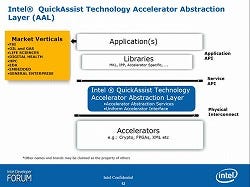

具体的な使い方としては、やはりXeonとの組み合わせということになる(Photo19)。FPGAアクセラレータを何個まで繋げられるのか、というのは明確にされていない。構成によっては、CPUが1つでFPGAが3つというのもありえそうに思うが、現状のAALがそれに対応しているか、というのがちょっと不明である。そのAALというのは、こんな構造をとるとしている(Photo20)。Windows NT系で言うところのHAL(Hardware Abstraction Layer)に相当するものをIntelが提供し、その上はアプリケーションが自由にアクセスできるようにする、という形になるのだろう。これは別にWindows NTのみではなく、Linux系などでも同様の仕組みは必要だから、複数のOS向けにこのAALが提供されるという形になると考えられる。ただこのAAL、実際に提供するのがどこか? というと恐らくは各デバイスベンダーだろう。AALはあくまでインタフェースの定義にとどまり、それに合わせて各デバイスベンダーがインプリメントしたものを、デバイスと一緒に提供する形になると思われる。

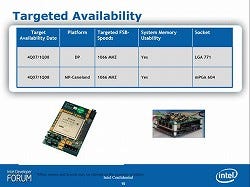

ところでちょっと気になるのは提供時期ではなく、FSBの方。Photo21に示すように2007年末~2008年初頭に、実際にアプリケーションベンダーはこれを使ったシステムを構築できるようになると見込まれるが、FSBが1066MHzどまりとなるのは、システムパフォーマンスを考えるとちょっと「?」マークがついてしまう。勿論現状のFPGAに1600MHzの信号を扱わせるのは(不可能ではないが)かなり無理があるので、それを考えればこの縛りはそれなりに意味はあるのだが、このFSBがそのままCPUにも適用されてしまうのが、ちょっと微妙な感じではある。

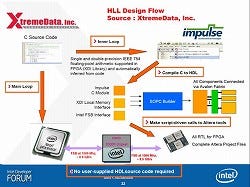

最後にこのFSB-FPGAの使い方の一例をちょっと紹介しておく。これはXtremeData, Inc.の提供する開発環境だが、もともとのソースコードをコンパイルする際に、Outer Loopはx86でそのまま処理し、Inner Loopに記載されるFloating Point演算をそのままHDLに変換、それをSOPC Builder経由でRTL化し、FPGAにダウンロードできる形式にするというもの。これにより、ユーザーがHDLを記述せずにFPGAを使えるというのがウリとなっているが、チューニングのフェーズに入るとこんなやり方では通用しないのは明白。とはいえ、とりあえず使うには便利なツールであろう。