ILLIAC IV

1962年にDaniel Slotnickらは、「Solomon(Simultaneous Operation Linked Ordinal MOdular Network)」という並列コンピュータを提案した。

Solomonコンピュータは32×32のPE(Processing Element)で構成され、それぞれのPEは1bit幅のシリアル演算器と32bit×128語のメモリを持つ。そして、全PEは制御ユニットから供給される同一の命令を実行するSIMD(Single Instruction Multiple Data)方式のコンピュータであった。ただし、Solomonは論文の発表だけで、実際のマシンは作られなかった。

その後、Slotnick氏はイリノイ大学のUrbana-Champaign校に移り、国防総省のDARPAの資金を得て開発したのが「ILLIAC IV」という並列コンピュータである。

Solomonのプロセサエレメント(PE)は1bitの演算器で、これでビットシリアルに計算を行う設計であったが、ILLIAC IVのPEは64bitの浮動小数点演算器を持ち、32bit浮動小数点数の演算や符号なし整数の演算も実行できるものであった。当初の計画ではILLIAC IVは256台のPEを持ち、全体では1GFlopsのピーク演算性能となるはずであった。

1966年2月にDARPAとの契約が交わされ、開発予算は800万ドルであった。開発主体はイリノイ大学であるが、ILLIAC IVの製造を請け負ったのはBurroughsである。また、Texas Instrumentsが高速のECLの中規模集積回路の開発を請け負った。

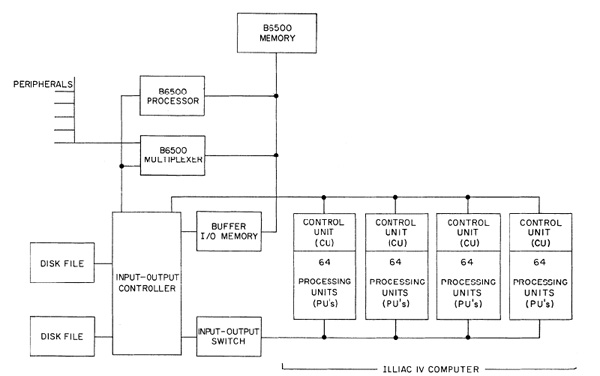

図3.2に示すように、ILLIAC IVは、BurroughsのB6500メインフレームを全体の制御とI/Oに使い、それにILLIAC IVアレイコンピュータを接続したという構造になっている。アレイコンピュータは64PEからなるQuadrantというユニット4台で256PEを構成していた。

-

図 3.2 ILLIAC IVシステム。BurroughsのB6500コンピュータを制御とI/O処理に使い、ILLIAC IV並列コンピュータを接続した構造になっている。256PEを持つ当初のシステムの図 (出典:Robert Davis、"The ILLIAC IV Processing Element"、 IEEE Trans. On Computer、 Vol. C-18、 No. 9、Sep 1969)

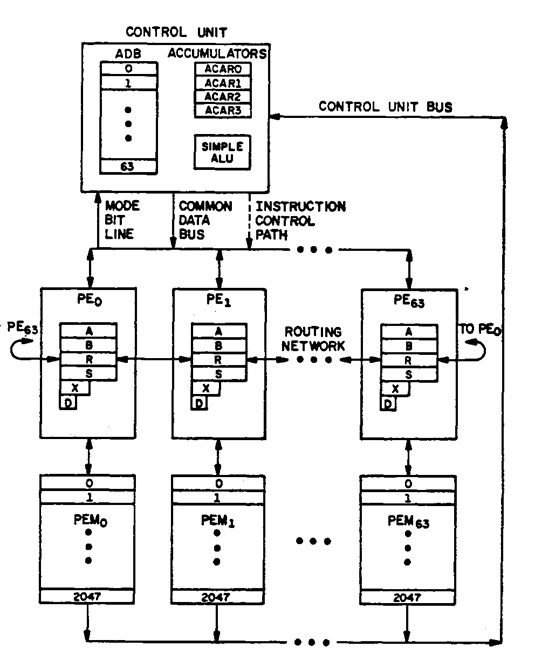

ILLIAC IVのQuadrantは図3.3のように、1つのCU(Control Unit)に64台のPEが接続され、64PEが同じ命令を実行するSIMDアーキテクチャになっていた。各PEはPEMと呼ぶ64bit×2048語のメモリを持ち、8×8の2次元メッシュで接続されていた。2次元メッシュはすべてのPEが直接繋がっているわけではないので、送信PEと受信PEの間に直接の通路が無い場合は、中間のPEを経由して通信を行う。クロックは20MHzで、1ホップの通信時間は1サイクルである。

図3.1のネットワークで言うと、メモリネットワークはPEとメモリの接続は1対1の直結で、PE間のネットワークも2次元メッシュという物量を抑えた構造になっている。

各PEは64bit浮動小数点演算器を持ち、64bit/32bit浮動小数点演算、あるいは64bit/8bitの符号なし整数演算を行うことができた。浮動小数点加減算(正規化なし)は5クロックを必要としたので、ピーク加算性能は256PE×20MHz/5Clock=1024MFlopsということになる。

なお、1969年に出された「CDC 7600」のピーク演算性能は36MFlopsであり、目標通りにできればILLIAC IVは圧倒的な高性能マシンとなるはずであった。

-

図3.3 ILLIAC IVアレイプロセサ 1Quodrant分。64個のプロセサに1対1で2048語のメモリPEM)が付き、全体を制御ユニットCUがコントロールする構造 (出典:W. Bouknight et. Al.、"The Illiac IV System"、Proc. of the IEEE、 Apr. 1972)

(次回は8月23日の掲載予定です)