米Micron Technologyは3月3日に容量256GBの「LPDRAM SOCAMM2」を発表した。これに関するオンラインの記者説明会が3月5日に開催されたので、この内容をご紹介したい。

SOCAMM2の容量を256GBに増量

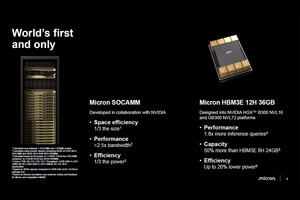

SOCAMMはMicronとNVIDIAの共同開発による独自のLPDDR5xベースのメモリモジュールで、2025年3月に発表された。これの改良型がSOCAMM2で、2025年10月にサンプル出荷がアナウンスされている。ただこの最初のSOCAMM2は容量192GBだった訳だが、今回これが256GBに増量された形になる。

そんなLPDRAM SCCAMM2だが、Micronは単にNVIDIA以外にもこれを販売していきたい事を匂わせる内容となった。まずマーケットの動向で言えば、サーバーの伸びに対してLPDDRの伸びがはるかに大きくなると予測される(Photo01)。

また性能面でも例えばTTFT(Time To First Token:最初のトークンが出力されるまでの時間)が192GBモジュールに比して2.3倍高速になる(Photo02)ほか、エージェント型のAIワークロードでも大幅に性能が改善される、としている(Photo03)。

-

Photo03:Photo02はNVIDIAのGrace Blackwellあたりを想定した図だったが、こちらは従来に無い製品。“Artist rendering of general-purpose server”という架空の製品向けという事だが、要するにそういう製品の登場を期待している訳だ。

実際に説明会では、1TBと2TBのシステムで100万ContextのLLMを実行した場合の動作のデモが行われ、2TBの方が圧倒的に高速であることが示された(Photo04)。

32Gビットダイの8枚積層で1チップあたり32GBを実現

ちなみにこの256GB SOCAMM2であるが、8チップ(SOCAMM2の両面実装)で構成されているのでチップあたり32GBとなるが、内部は32Gビットダイの8枚積層構造である(Photo05)。

この32Gビットダイは、192GB品と同じく1γ nmプロセスで製造されているが、1β nmプロセスの製品と比較して効率が倍(つまり消費電力を変えずに容量を2倍)にしたとされる。

Micronは今後、2035年には月間あたりのトークン数が16万Trillion(16京)に達する予測としており、こうしたニーズに応えられるのはLPDDR系であると締めくくった(Photo07)。

すでに顧客へのサンプル出荷は開始済み

気になるのは、すでに業界はLPDDR5xからLPDDR6に移行しつつあり、質問でもQualcommがすでにLPDDR6xのテストを行っている事についての見解が問われていた。ただSOCAMM2はJEDECが標準規格として仕様策定中なものなので、勝手にLPDDR6/6xに移行する訳にもいかない。もちろん通常版のDDR5を使うよりも省フットプリント・省電力ではあるのだが、どこまでNVIDIA以外のユーザーを獲得できるか次第ではある様に思われる。とりあえず今回発表の256GB SOCAMM2はすでに顧客にサンプル出荷中で、量産開始は今年下半期中を予定しているとの事であった。