imecは2月17日、米国サンフランシスコで開催中の半導体の国際会議「国際固体回路会議(ISSCC 2026)」にて、250μm×250μmの小フットプリントを実現しつつ、1サンプルあたり2.2pJという低変換エネルギーを実現した7ビット、175GS/sの大規模タイムインターリーブ・スロープアナログ・デジタルコンバータ(ADC)を発表したことを明らかにした。

AIやクラウドの活用で増大するデータ容量の送受信に対応するために光通信ネットワークの速度の向上が図られているが、サンプリングレートが100GS/sを超えると、光トランシーバーに不可欠な有線通信用ADCなどの基盤コンポーネントが大型化し、相互接続の長距離化に伴う寄生容量の増加やエネルギー損失が課題となっている。

歪み補正とスイッチド入力バッファの採用で低変換エネルギーと小フットプリントを実現

こうした課題に対して、世界各国で解決に向けた研究開発が進められており、imecも2024年のISSCC(ISSCC 2024)にて、従来設計比で少なくとも2倍の高集積化を実現しつつ、高い電力効率を備えた大規模タイムインターリーブ・スロープADCアーキテクチャの報告を行っていた。今回の研究成果は、この取り組みをベースに、超高速サンプリング時でも高精度な信号変換と広帯域幅を確保できるように技術の発展を行ったものだという。

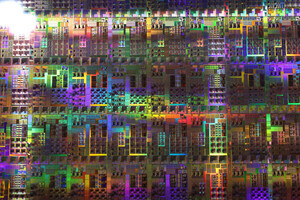

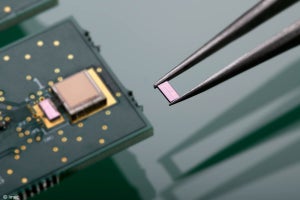

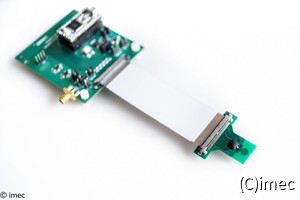

具体的には、傾斜信号を形成する新しい線形化アプローチの採用による歪みの補正と、スイッチド入力バッファにより、ADCの2048チャネルのタイムインターリーブ・アレイへ効率的にデータを供給し、電気的負荷を最小限に抑えることで、信号の完全性を損なうことなく超高速サンプリングを可能にしたとのことで、5nm FinFETプロセスで製造された試作回路では、7ビットかつ175GS/sのADCを250μm×250μmの小面積コア領域と1サンプルあたり2.2pJの低変換エネルギーの両立ができることが確認できたとする。

なお、imecでは、今回の成果について面積および消費電力の効率最大化が求められるデジタル集約型有線相互接続の高度化に向け、有力なソリューションとなるとしており、現在、3nmプロセス世代をベースとした後継の設計を行っているとするほか、さらなる先端プロセスを高性能な有線通信用データ・コンバータ設計にどのように活用できるかについて、14オングストロームの設計可能性も検討しているとコメントしている。