イメージセンサのウェハボンディング技術をCPOに応用

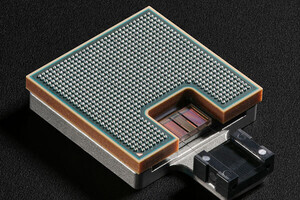

Tower Semiconductorは11月12日、積層型BSIイメージセンサ向けとしてすでに量産実績を有する300mmウェハボンディング技術を拡張し、シリコンフォトニクス(SiPho)やSiGe BiCMOSプロセスを組み合わせたヘテロジニアス3D-ICインテグレーションを可能にする新技術を発表した。

同技術を活用することで、SiPho(PIC:フォトニックIC)やSiGe(EIC:エレクトロニックIC)を組み合わせるといった異種類のプロセス技術で実装された各種機能ウェハを積層し、ウェハレベルで完全に統合された3D-ICを実現することができるようになると同社では説明しており、PICとEICを融合するCo-Packaged Optics(CPO)など、コンパクトかつ高性能なインテグレーションが求められる新しいアプリケーション分野のサポートが可能になるとする。

Cadenceと協力して開発

また、同プロセス技術の補完として、Cadence Design Systemsと協力し、統一された設計環境内で複数のプロセス技術の共同シミュレーションと共同検証を可能にするVirtuoso Studio Heterogeneous Integrationフローを拡張。このサポートにより、複数のPDKを同時に使用する必要があるウェハスケール3D統合をイメージセンサ以外の分野でもリファレンスフローとして利用できるようにしたという。具体的には、設計者が単一のCadenceの設計プロジェクト内で、複数の技術プラットフォームから構築された3D-ICおよびウェハボンディングチップのレイアウト、接続性チェック、完全なシミュレーションを可能としたとのことで、これにより異なる技術で作られた複雑な積層チップ製造における初回成功率を向上させることができるようになったとしている。

なお、Towerでは、今回の拡張により、3D-ICおよびヘテロジニアス統合におけるリーダーシップを強化し、次世代市場全体でのイノベーションを加速する先進的なアナログソリューションを提供していくとコメントしている。