日本でGAAトランジスタの製造が可能に

産業技術総合研究所(産総研)は11月5日、2nmをはじめとする先端ロジック半導体で活用されるトランジスタ構造「ゲートオールアラウンド(GAA)」を独自技術に基づき実現するとともに、企業などが利用可能な共用パイロットラインを確立したことを発表した。

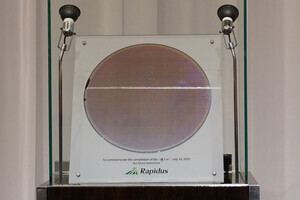

これは産総研 先端半導体研究センターが、新エネルギー・産業技術総合開発機構(NECO)の助成事業の元、国内の半導体製造装置メーカーである東京エレクトロン(TEL)、SCREENセミコンダクターソリューションズ、キヤノンとの共同研究による成果で、同パイロットラインを用いることで、半導体製造装置や半導体材料メーカーなどが、300mmウェハ上にGAAトランジスタ構造を試作し、技術の検証を行うことが可能になるという。

先端プロセス向け要素技術開発で必要となる試作ラインを構築

半導体の演算回路を構成するトランジスタの構造は、プロセスの微細化に伴い、従来のプレーナ型からFinFETへと変化し、2-3nmプロセス世代からは多段の極薄膜シリコンチャネル(シリコンナノシート)をゲートで包むGAA構造への移行が進んでいる。すでに一部ファウンドリでGAA構造トランジスタを用いたロジック半導体の製造が行われているが、こうした複雑な立体構造を持つトランジスタの実現には、従来に増して高度なプロセス技術が要求されるほか、多額の設備投資ならびに研究開発費が必要とされ、高い国際競争力を有している日本の半導体製造装置メーカーや半導体材料メーカーであっても単独でGAAトランジスタの試作と、自社開発の新技術の検証を行うことは難しい状況となっていた。

しかし国内にはそうした試作検証可能な設備がなく、また、海外機関の試作設備を使用する場合には、ノウハウを含む知財などの機微情報に海外機関が関わらざるを得ないという状況であったことを踏まえ、産総研先端半導体研究センターがNEDOの助成事業「先端半導体の前工程技術(More Moore技術)の開発」に対応した共同研究として「先端3次元構造ロジック半導体デバイスの製造・プロセス技術の開発と検証用パイロットライン整備」を推進。TEL、SCREEN、キヤノンと協力する形で企業などが活用可能な産総研スーパークリーンルームに新規に16台の最先端装置を導入し、300mmウェハ対応の共用パイロットラインの構築を進めてきたという。

GAA構造トランジスタの正常な動作も確認

この300mmパイロットラインには、産総研が設計した性能仕様に基づいた最先端の半導体製造装置が新たに導入され、それぞれのプロセスレシピの開発とGAA構造トランジスタの試作に必要な要素プロセスが確立されたとする。具体的には、「多段シリコンナノシートを形成するシリコン・シリコンゲルマニウム結晶膜成膜技術」、「シリコンナノシート層のみを残してシリコンゲルマニウム層を選択エッチングする技術」、「シリコンナノシートを囲むゲート絶縁膜とゲート金属電極を堆積させる成膜技術」、「トランジスタのしきい値を制御するためのゲート絶縁膜厚と金属膜厚を精密に調整する原子層堆積(ALD)技術」などが必要であったとのことで、これらのプロセスが新たに開発されたという。

すべての要素プロセスは、パートナーである半導体製造装置メーカー3社と個別に連携して開発が進められ、特にGAA構造トランジスタ形成の主要工程となる、シリコン・シリコンゲルマニウムエッチング工程、高誘電率ゲート絶縁膜・金属ゲート電極構造の形成工程は、各社から産総研への人材の派遣も含め、それぞれ密接な連携の元で開発が進められたとするほか、開発されたプロセスはプロセスモジュールとして活用できる形で整備され、すべてのプロセスは産総研が適切にノウハウ管理し、パイロットラインを利用する企業などが制約なく最先端トランジスタ構造を試作し、技術の検証ができるようにしたという。ちなみに同パイロットラインについては、GAA構造トランジスタの試作のみならず、前世代のFinFET型トランジスタなど、プロセスモジュールを活用できる他の試作実証も可能だという。

実際に産総研がGAA構造トランジスタの試作に必要な要素プロセスを統合し、一連の製造工程を実施して試作を行い、その動作を確認したところ、ゲート電極の断面電子顕微鏡写真よりシリコンナノシートの周りをゲート絶縁膜とゲート電極が取り囲んでいる形状が、ソース・チャネル・ドレインを横切る断面電子顕微鏡写真よりシリコンナノシートがソース・ドレイン電極に正しく接続されていることが確認できたとするほか、電気特性評価の結果からはゲート電圧の印加によりドレイン電流がon-off制御される正常な電流電圧特性が得られていることが確認されたとしている。

次世代のトランジスタ構造の試作も検討

これらの成果を踏まえることで、国内企業や大学などが独自のプロセス技術開発を行い300mmパイロットラインを活用した試作を実施することで、独自プロセスを適用した最先端トランジスタ構造の性能面での良否を評価することが可能となると産総研では説明している。具体的には、半導体製造装置メーカーが自社開発のプロセス装置の処理工程を組み合わせたり、半導体材料メーカーが自社開発の材料を必要なGAAトランジスタ製造工程に適用して適合性や性能の検証を行うことが可能になるとしている。また、同パイロットラインでは、試作プロセスの提供のみならず、試作したトランジスタの電気的評価やプロセス途中の各種物理分析手法も提供可能であるともしている。

なお、産総研ではこれまでに「先端半導体製造技術コンソーシアム」を設立し、同コンソーシアムにおいてパイロットラインの利用に係るノウハウなどの共用知財の取り扱いルールを整備してきたとのことで、すでに同コンソーシアムには5法人がライン利用を目的に入会しているとするほか、パートナー3社によるパイロットライン活用もすでに進んでいるとする。また、パイロットラインを活用する企業・大学などの研究者や技術者が産総研スーパークリーンルームで活動することで、先端半導体製造技術に係る若手人材育成にもつなげていきたいとしている。

さらに技術的にも、今後はゲート電極の寸法の微細化、ならびにnチャネル型トランジスタとpチャネル型トランジスタの両方を実現するCMOS化など、要素プロセスの高度化と拡充を進め、トランジスタ性能や信頼性の向上、また低消費電力化に資する技術の創出を目指すとしているほか、300mmパイロットラインを利用した企業などとの共同研究を推進し、今回の成果の普及を進めていくとしている。加えて、CFETのような将来世代の新構造・新材料デバイスの試作や高周波アナログ素子開発、新材料チャネル・多機能デバイスを搭載した回路試作なども可能なプラットフォームへの拡張についても目指していきたいとしている。