英Armは9月10日、従来のCortexに変わる新しいクライアント向けのプラットフォームとして「Lumex CSS」を発表した。これに関する説明がオンラインの形で行われたので、その内容をご紹介したい。

SME2をサポートしたCPU「C1」

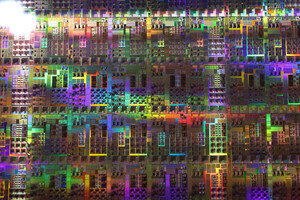

今年5月に発表があったように、Armは製品市場別に異なるブランドを利用する事を発表しており、その第1弾が6月にアナウンスされた「Zena CSS」だった訳だが、今回はこれに続きクライアント向けのLumexである(Photo01)。

今回発表されたLumex CSSは「C1-Ultra/C1-Pro」という2種類のCPUコアと「Mali G1-Ultra」というGPUコア、それとL1 Cacheを含む周辺回路から構成されるCSS(Compute Sub System) Platformとなる。

C1 Coreの詳細は後述するとして、C1 CPUの最大の特徴はSME2のサポートである。まずSME2の基になるSMEだが、これはSVE2の拡張オプション的な扱いである。SVE2は御存じの通りベクタサイズを変更可能なSIMD演算命令であるが、行列演算は分解して処理を順次行うしかない。そこで、SVEのRegisterをそのまま利用しながら行列計算、というか外積を行えるようにしたのがSME(Scalable Matrix Extension)である。実際にはこの外積を行うにあたり、中間結果を保存する領域が必要である。そこでSMEでは「ZA」と呼ばれる新しいMatrix Storageを追加、これを利用して外積の計算を行うという仕組みである(Photo03)。

このSME、実は2022年の2月には仕様が公開されていた。もっとも仕様だけあっても実際にSMEを実行できるコアが無ければ意味が無いのだが、最初にこれを実装したのはApple M4である。逆に言えばArmのコアは長らくこのSMEを実装していなかったのだが、今回仕様をSME2に拡張してC1 Coreに実装した格好になる。そのSMEとSME2の違いであるが、SMEは外積を含む一部の行列演算の高速化のみを想定していたのに対し、SME2ではより広範なアプリケーションに対応する事を想定しており、マルチベクトルデータ処理命令、マルチベクトルに対するロード/ストア、マルチベクトル予測機構などが導入された。

具体的には

- Zベクトルを乗数・被乗数入力とし、結果をZA配列ベクトルに蓄積するマルチベクトル乗算積算命令の追加

- 複数のSVE ZベクトルをSource/Destination Registerとして使用し、ZAを利用するSME2命令の入力前処理・出力後処理を行うマルチベクトルロード/ストア/移動/置換/変換命令の追加

- 従来のSVE Predication機構を拡張し、複数のVector Registerを制御できるPredicate-as-counter機構

- 専用ルックアップテーブル命令と外積命令を用いたNeural Networkの圧縮機能(Binary Neural Networkを含む)

- SME2のLookup Table機能をサポートする512ビットのアーキテクチャレジスタZT0の追加

などが変更項目として挙げられている。

SME2ユニットはCPUコアとは別に実装

さて、ArmはこのSME2を説明するにあたり、"CPU Cluster with SME2"という言い方をしている(Photo04)。

-

Photo04:ちなみに説明の中ではInt 4とかInt 2のサポートという話があったが、SVE2にInt 4やInt 2が追加されたという話ではないので、これはCompressed neural networkの機能と思われる

つまりSME2ユニットは、丁度IntelのAMXユニットの様に、CPUコアとは別に実装される形になっている(Photo04)。実はSMEの時にはImplementation optionsとしてShared TypeとBuild-in(というかDedicated Type)の2種類が提示されていたのだが、Apple M4がどちらを実装したのかは明らかではない。ただSMXはZA Vectorが結構な面積を喰う上に演算ユニットもかなりのサイズになるので、Dedicated Typeは正直現実的ではない。実際SME2 Unitのエリアサイズを確認したところ「C1-Proコアと同等」という返事であり、現実問題としてShared Typeしか選択肢はないだろう。ちなみに今回のC1 CPU ClusterにはSME2ユニットは1つだけだが、次世代のC2は2つに増やす計画があるという話であった。

-

Photo05:Shared Typeの場合、複数のコアからSMEを共有する関係で、この調停機構をどんな形で実装するのかが1つ難しいポイントになりそうだが、それをH/WでやるのかS/Wでやるのか、はスライドには記されていない

ところでShared Typeの場合、各コアとSME2ユニットがどう同期を取るのか? という問題が出てくる。SME2の内部構造はこんな具合(Photo06)で、ほぼ単体で動作する様に見える。

-

Photo06:Arm C1-Scalable Matrix Extension 2 Technical Reference ManualのC1-SME2 unit componentsより。WritebackはZA Vectorに行う形になるから、あとはそれをSME2 unit Bridge経由でCPUコアに送り出す格好と思われる

なのでAccelerator的に利用するのかと思ったのだが、これを確認したところ返答は"Instruction DecoderがSME2命令を認識して、通常の命令と同様に内部のSME2専用実行パイプラインにDispatchします。"という返答が戻ってきた。ただ、だとすると「ではPhoto06のDecode/issueやExecution pipelineは何をやってるんだ?」という疑問を禁じ得ない。あるいは、各コアがSME2命令を認識した場合、その命令をSME2 unit Bridge経由でSME2のInstruction Decodeに投げると同時に、SME2を実行中であることをScoreboardに記録し、SME2から結果が返ってくるまでその状態を保持すると共に、利用するSVE Registerにロックを掛けるといった形でSME2との同期を取る仕組みが実装されているのかもしれない。ただそうだとすると、いよいよ複数のC1コアの間でSME2を共有する際の排他制御が重要になってきそうである。

C1シリーズは4種類だがLumexの名称はC1-Ultra/C1-Premiumに適用

長々とSME2の話をしたのは、今回のLumix CSSの目玉がまさしくSME2であり、特にAI性能の改善はこのSME2に集中しているからである。Arm C1シリーズのCPUは、Premium向けのC1-Ultra、Sub-FlagshipのC1-Premium、それとHigh-EndのC1-Pro、LittleコアのC1-Nanoの4種類が用意されるとしている。面白いのはLumexのブランドを名乗れるのは、C1-UltraあるいはC1-Premiumのどちらかのコアを1つ以上搭載している場合で、逆に言えばC1-ProとC1-NanoだけのSoCはLumexを名乗れないという話であった。

-

Photo07:C1-UltraがCortex-Xシリーズ相当、C1-PremiumがCortex-A700シリーズにあたる。C1 Proは言ってみればCortex-A600位のレンジ向け、そしてC1-NanoがCortex-A500相当になる格好だ。最初はC1-NanoがCortex-A300の後継かと思ったが、違う模様

そのC1-Ultraは「デバイスレベル」でCortex-A925より25%高速という話だが、それよりもSME2を利用する事でAI性能が5倍に跳ね上がる、という方が数字としては当然インパクトがある。実際にAI処理を実行する際の性能は2.8倍~4.7倍と当然処理によって差は出るものの、大幅に性能が向上するとしている。

どうもArmはAI時代をCPUだけで乗り切る方向に舵を切ったようだ。「NPUやGPUは性能は高いが、最適化は難しいしインプリメントも遅い」とその理由を語ったが、要するにArmのGPUやNPUはAIアプリケーション開発者によるインプリメントの優先順位が低く、であればCPUを高速化した方が使って貰いやすいという判断になったものと思われる。余談だが、C1-PremiumはC1-Ultraと比べ整数演算性能は6%程度劣るものの、エリアサイズが35%程度削減されるとの事。またC1-Nanoは、前世代のCortex-A520より整数演算性能で5から6%程度の性能向上が果たされているとされる。

全シリーズにRay Tracing Unitが搭載されるMali-G1

これに加えて、GPUも今回Mali-G1 Ultraがリリース。グラフィック性能とAI/ML性能が20%増、Ray Tracing性能は2倍になったとする(Photo10)。

このRay Tracingに関しては、それを利用するゲームでのフレームレートが最大40%向上するとしている(Photo11)。

-

Photo11:ただこの数字、RTUv1(Ray Tracing Unit v1)という事は、比較対象はImmortalis-G925ではなく2022年リリースのImmortalis-G715との比較の可能性がある

なお今回はMali G1-Ultraのみが紹介されたが、他に「Mali-G1 Premium/Pro」も用意されている(Nanoはない模様)との事。またすべてのMali-G1がRay Tracing Unitを搭載しているという話であったが、流石にローエンドのMali-G1 ProのRay Tracingはかなり厳しいとの事だった。

AIの処理内容次第ではGPUよりもCPU+SME2の方が高速に

ところで再びAIの話に戻るのだが、今回のLumex CSSの場合、必ずしもMali-G1 UltraにAI処理をさせるのが最高速とは限らない、というのがこちらのグラフ(Photo12)。

横軸はモデルの複雑さ、縦軸が相対性能である。複雑な大規模モデルになると、C1-ProにSME2を組み合わせても、Mali-G1 Ultraにはかなわないのだが、小規模なモデルに関してはC1-ProにSME2を組み合わせた方がMali-G1 Ultraにやらせるよりも高速、という結果が出たとしている(Photo12)。

このLumex CSS、単にIPだけではなくPhysical Implementationの提供が行われる(Photo13)。

こちらはGDS IIでの提供となるという話だ。対象となるのは3nmプロセスで、複数のファウンドリということで、TSMCとSamsungはほぼ確定として、Intel Foundry向けの提供予定があるかどうかは公開されなかった。もうPOPとかでは追い付かないという事なのだろうが、この時期にハードIPというのはなかなか考えさせるものがある。

なお、Armは同日よりこのLumex CSSのライセンス提供を開始しているとの事であった。