極薄チップを高スループットで実装する技術を開発

東レエンジニアリングと新エネルギー・産業技術総合開発機構(NEDO)は8月28日、NEDOの助成事業「ポスト5G情報通信システム基盤強化研究開発事業」において、東レエンジニアリングがポスト5G情報通信システムで用いる先端半導体や次世代光集積回路の量産に向けて、極薄チップを高スループットで実装する技術を開発したことを発表した。

半導体のさらなる高性能化、低電力化の実現に向けて、チップに対する薄化が求められるようになっている。しかし、半導体チップは厚み20μm以下になるとハンドリング時の歩留まりが低下してしまうため、薄化しつつも量産で求められるスループットを実現できるハンドリング技術の確立が求められていた。

レーザーをチップに照射して高歩留まりの転写を実現

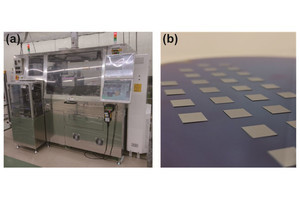

今回、東レエンジニアリングではこうした課題の解決に向けて、独自の高精度レーザー加工位置制御技術とレーザー転写プロセスに最適化したレーザー光学系を開発。これらを組み合わせることで、微小なレーザー光を、チップの端部から順に照射することで、極薄チップを高い歩留まりでキャリア基板から剥離させ、キャッチ基板に転写する「スキャン方式」を開発。独自のレーザー加工技術を用いてレーザー光のスキャンパターンを最適化することで剥離中のチップの姿勢を安定化することを可能としたため、転写位置精度と歩留まり、スループットを高い水準でバランスさせた実装が可能となったという。

実際に、チップサイズ5mm×5mm、厚み10μmで試作された半導体チップに対する実証試験では、精度±2μm(3σ)で転写することに成功したとするほか、転写したチップの外観検査や抗折強度測定からチップに有意なダメージがないことも確認したとする。このほか、チップサイズ0.15mm×0.70mm、厚み1μm以下のInPなどの化合物チップの転写とシリコン基板への接合にも成功するなど、化合物チップの実装プロセスへの適用も可能であることも実証したとのことで、従来比10倍以上の効率で生産できることを確認したとする。

515mm×510mmのパネル基板にも適用可能

なお、同技術は300mmウェハ以外にも515mm×500mmのパネルサイズにも対応しているとのことで、さまざまなデバイスへの極薄チップの実装評価が可能なことから、東レエンジニアリングでは、同技術を活用し、先端半導体の製品化に向けて、さらなる技術の改善と最適化を行いつつ、半導体メーカーや関連企業、機関との連携を進めていくことで、同技術の実用化に向けた取り組みを進めていくとしている。