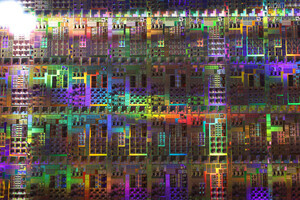

レゾナックは2月12日、半導体のパッケージを大型化した場合に生じる課題の1つである「反り」を抑制した、次世代半導体パッケージ向け低熱膨張銅張積層板を開発したことを発表した。

半導体のパッケージ基板はチップレットをはじめとする複数のチップを積層することで高性能化が進んでいるが、大型化に伴って基板に反りが生じ、信頼性が低下するリスクが生じやすくなっている。そうした基板の反りを抑制するためには、基板のコア材料である銅張積層板の熱膨張係数を小さくすることが求められるが、そうすると今度は温度サイクル試験の冷却時に、基板を構成する他の材料との熱膨張差により、クラックが発生しやすくなるという課題があった。

そうしたクラックの低減に向けて、弾性率を低くするなどといった銅張積層板の設計指針を示すことはできるものの、実際の銅張積層板は樹脂や無機材(ガラスクロス)などといった複数の材料から構成されており、各材料個別の設計指針にまで落とし込むことは難しかったという。

そこで同社の計算情報科学研究センターは今回、そうした問題の解決に向けて、銅張積層板の樹脂とガラスクロスから成るコア層に、スケールの異なる構造体同士の物性や挙動の相互作用を考慮できる有限要素法である「マルチスケールFEM(Finite Element Method)解析」を適用することで、クラックが発生しやすい、コア層の樹脂にかかる局所的な応力を詳細に解析し、樹脂の特定の物性を制御することで、発生する応力を低減した銅張積層板を開発することに成功したとする。

実際に、開発された製品を温度サイクル試験にかけたところ、寿命が従来比4倍に伸びたことを確認したという。

また、この成果を受けて同社では、同技術を活用して、汎用的な物性可視化システムを構築、社内展開を開始したとしている。このシステムでは、銅張積層板に限らず、封止材やフィルム材料など複数材料から成る幅広い製品に対して、ユーザーが材料の物性を入力すると、目的特性(例として反り)がどのように変化するのか、その傾向を可視化することができるようになるという。

なお、同社では同技術について100mm×100mmを超える半導体パッケージにも対応できるとしており、2026年の量産開始を目指すとしているほか、同システムについても強みとする半導体後工程製品を中心にすでに活用を開始したと説明している。