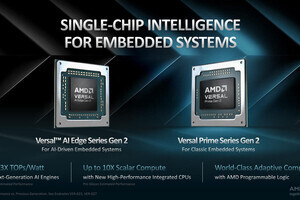

米AMDは11月12日、幅広いワークロードにおいて最高レベルのシステム加速を実現するために設計されたアダプティブSoCプラットフォーム「Versal Premium Series Gen 2」を発表した。オンラインでの記者説明会の資料に基づき、この内容をご紹介したい。

Versal Premiumの第1世代は2020年3月に発表された。当時のターゲットはネットワーク向けであり、それもあって特にI/Oの充実が図られた構成になっていた訳だが、Gen 2にあたってはメモリ帯域の増大とCXL Attached Memoryへの対応が図られることになった(Photo01)。

-

Photo01:DRAMeXchangeでDRAM Spot priceを見るとDDR5-4800/5600 16Gビットが平均4.804ドル、DDR4-3200 16Gビットが同3.163~3.225ドルで、まだBit crossには至っていないが、そろそろDRAMベンダー各社ともDDR5がメインになってきているのは間違いない

またネットワーク機器に関しては、5GへのDeployが一段落し、Advanced 5Gや6Gはもう少し先になる一方で、HPCやAI向けのニーズが高まる事になった(Photo02)。

-

Photo02:実を言えばNetworkもHPC/AIも、要素を分解すると求めるニーズはあまり違わず、強いて言えばPCIe Gen6/LPDDR/CXLといった標準規格へのニーズが高まっているのが違う程度か

こうしたニーズに対応して今回発表されたのがVersal Premium Series Gen 2である。大きな違いは

- LPDDR5X/DDR5の対応

- PCIe Gen6に対応

- CXL 3.1に対応し、Type 3(CXL Memory)を利用できる様になった

- PCIe IDE(Integrity & Data Encryption)を始めとするSecurity強化

- GTM2 Transceiverを搭載

あたりが主なものとなる。

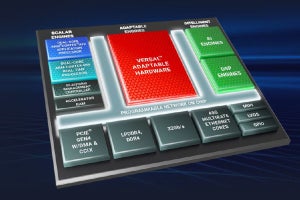

後で細かい仕様(Product Table)も出てくるが、System Logic CellとかLUTなどは既存のVersal Premiumとそう大きくは変わっていない。

-

Photo03:Versal Premiumでは複数ダイをCoWoSで接続しているイメージの写真があったが、Gen 2ではまるでMonolithicに見える。ただ恐らくこちらもSKUによっては複数ダイでの構成になるだろう

Photo03をもう少しBreakdownしたのがこちら(Photo04)。

初代Versal Premiumだとハイエンドは16×PCIe Gen5×4(合計64レーン)が使えるからこれには見劣りするが、メインストリーム製品は2×PCIe Gen5×8だったのが今回2×PCIe Gen6×8になったとか、LPDDR5/DDR5を最大8ch利用できる、あるいはHigh-Speed MIPIのPHYを搭載するなど、かなりHostとのConnectivityを強化した感がある。といっても、基本は既存のVersal Premiumの延長にあるとしており(Photo05)、逆に言えば既存のVersal Premium向けのIPはほぼそのまま利用できる様だ。

Photo06がより詳細な構成で、水色の部分が今回追加されたものとなる。

さてまずMemoryについて。今回のVersal Premium Gen 2では最大8chのDDR5/LPDDR5XのI/Fを搭載する。これを利用してCXL Type-3、つまりCXL Attached Memoryを簡単に構成できる様になった(Photo07)。

サポートされるはDDR5-6400とLPDDR5X-8533で、これはDDR4-3200とLPDDR4X-4266だったVersal Premiumの倍の帯域となる。その一方で、帯域当たりの消費電力は20~30%下がるので、結果としてより効率よく動作することになる。

LPDDR5Xの場合、最大8533Mbpsで、メモリが8ch(合計256bit幅)なのでメモリ帯域は273GB/sec。一方PCIe Gen6の方は64Gbps×16laneで128GB/secでしかなく、CXL Memory Moduleを構成する場合Memory BandwidthはOverkillとも言える。ただLPDDR5Xを使う場合、メモリ容量はどうしても少なめである。例えば現状SamsungのLPDDR5Xだと128Gbitなら×32構成で8533Mbpsの製品がある。これを利用すると128GBほどの容量になる計算で、ちょっと物足りない。これがDDR5を使うと、速度こそ最大でも6400Mbpsになるから204.8GB/secに抑えられる(それでもPCIe 6.0×16の帯域よりは大きい)が、容量32Gビットで×4構成のものがあるから256GB構成が可能になる。もし帯域を4400Mbpsまで落とす(この場合メモリ帯域は140.8GB/secまで落ちる)と、技術的には1chに2つのチップを接続できる(Versal Premiumでこの構成をサポートしているかどうかは現状不明)から、容量は倍の512GBが確保できる計算になる。今後、DRAMの容量増加によって64Gビットチップが利用可能になれば、1TB構成も夢ではないことになる。ただこの辺はVersal Premier Gen 2がどこまでサポートしているか次第であり、現在問い合わせを掛けている最中である。

2024年11月14日追記:AMDより、最大容量は1TBになる旨の返答が届いた。やはり筆者の想定通り、DDR5-6400だと最大512MB、DDR5-4400まで落とすと1TBの構成が可能になるようだ。

-

Photo08:また地味なところで、ECCおよびEncryptionのサポートが追加されたのも大きい。Enterprise向けではこれらは絶対に必要である。もっと言えばChipKillとかのサポートもあれば完璧なのだろうが、これに関してはCXL Memoryは(OSがサポートしていればH/W的には)Hot Plug&Unplugが可能だから、故障を起こしたモジュールは交換で済むとも言える

-

Photo09:Photo07の下側の構成のものを、E3.SなりEDSFFなりで構成するという格好である。「発熱が大丈夫なのか?」というのがちょっと気になるところではある。ちなみに500GB/secはLPDDR5Xの270GBに加え、CXLをHost Mode(HostのメモリをDeviceで利用する)で動作させた場合、128GB/secの双方向(全二重なので)で合計256GB/secとなり、合算すると500GB/secを超えるという事だそうだ

またPCI Express周りに関しては、PCIe Gen6対応のCPM6が実装されており(Photo10)、これを利用してPCIe Gen6.0に対応が可能である。

ちなみにFLITはこのCPM6内に実装されているが、後述するPCIe Gen7.0動作時にPCM6のFLIT機能が利用できるのかどうかは不明である。またこのCPM6を使わずに、直接TransceiverとProgrammable Logicが通信するGT Directモードも搭載されている。

GTM2(Photo11)は、普通に使う場合は最大で112Gbpsで、これはGTMと違いがない。

異なるのは、

- PCIe Gen7.0のテスト用機材向けに、特定のSKUではPAM4で128Gbpsの送受信をサポート

- 1.25Gbps~112Gbpsまで複数の転送速度をサポート

という辺りである。

また今回はこれに組み合わせるEnd-to-End Security機能も大幅に拡充された(Photo12)。

特にEncryption Engine(Photo13)、Network Processorの類では珍しくないが、FPGAで搭載されるのは確かに初めてかもしれない。

-

Photo13:考えてみれば、これ初代のVersal Premiumに搭載されていても不思議ではないのだが、ベースステーションとバックエンドの間とかはそもそも専用回線だから暗号化の必要が無かったという事なのかもしれない

AMDでは、例えばGPU ClusterのバックエンドにVersal Premium Gen 2を使う様なケースがある事も考えている様だ(Photo14)。

-

Photo14:AMDだとCluster内のGPU同士は独自のInfinity Fabricで接続するので、そのClusterから外部に接続するときのEthernetをVersal Premium Gen2に任せるという事だろう(Versal Premium Gen2とGPUの間はPCIe/CXLでの接続となる)

これに向けてEthernetの合計帯域を倍にした格好だ(400G×2として使うか、200G×4として使うか、あるいは100G×8とするかは構成次第であろうが)。

実際にVersal Premium Gen 2を利用したVPX-3Uのサンプル例がこちら(Photo15)で、従来と同じフォームファクタで帯域と計算能力を倍増させられる、とする。

-

Photo15:LDPCのデコーダはDVB-S2X(衛星デジタル放送用の拡張規格)に準拠したもので、従来はPL+DSPを使って実装していたが、性能/消費電力比を考えると専用ロジックを実装した方が良いと判断されたのだろう

これは通信とかレーダー、測定機器など様々な用途で有用なもので、その意味では初代Versal Premiumのマーケット向けの機能が削られた訳ではない。むしろLPDDR5Xのサポートとかより柔軟性に富むTransceiverの搭載などで、使いやすくなったともいえる。なおこのVersal Premium Gen 2に併せて、Vivadoの方も色々追加機能が予定されているとの事だ(Photo16)。

-

Photo16:ただしここに挙げられたものはいずれもVersal向けであって、Virtex/Kintex/Artix/Zynqなどの従来のFPGA製品に関しては、特に恩恵は受けられないとの事。ちょっと残念である

Photo17がとりあえずのVersal Premium Gen 2のProduct Tableである。初代Veral PremiumのTableと比較するとまだ品種が少ないというか、Logic Cellは最大でも3720K程度で、初代は最大18507K LCがラインナップされていた事を考えるとやや少ないというか、とりあえずはミドルレンジ向けを用意したという感じである。

ついでにPhoto04で“High DSP-to-LUT Ratio”とあったので実際に計算してみると表の通りで、確かにGen 2になってDSP1個あたりのLUT数はやや増えている(Gen 1の方はSKUで大きくばらつきがあるので、「やや」か「大幅に」かは難しいが)のが判る。ただ現状のVersal Premium Gen 2のSKUにはAI Engineを搭載したものが見当たらないのは、今後追加の予定なのか、それともVersal Premium Gen 2はAI Engineは積まない方針なのか、定かではない。

このVersal Premium Gen 2、2024年中にドキュメントとPower Estimation Toolがリリースされるが、Vivadoのサポートは2025年後半、シリコンは2026年投入の予定となっている(Photo18)。