大阪大学(阪大)と富士通は8月28日、量子コンピュータの早期実用化に向けて、共同開発している高効率位相回転ゲート式量子計算アーキテクチャ「STARアーキテクチャ」について、位相回転操作時の位相角の精度を向上させる技術、および量子ビットの効率的な操作手順を自動生成する技術を開発したことを共同で発表した。

同成果は、阪大 量子情報・量子生命研究センターの藤井啓祐教授(同・大学大学院 基礎工学研究科 システム創成専攻電子光科学領域 量子コンピューティング研究グループ兼任)、富士通らの研究チームによるもの。

量子ゲート式量子コンピュータは、さまざまな分野で現行コンピュータよりも遥かに短時間で回答を得られるとして期待されているが、計算中にエラーが発生しやすい点が課題だという。つまり、正確な計算を行うためには、大量の量子ビットを使ってエラーを防止する必要がある。実用的な計算を現実的な時間内で行うには100万量子ビットが必要と試算されており(FeMoco(酵素活性中心)のエネルギー推定問題をエラー率0.1%の条件下で解くために必要な量子ビット数の試算結果)、その実現にはかなりの年月を要すると予想されていた。

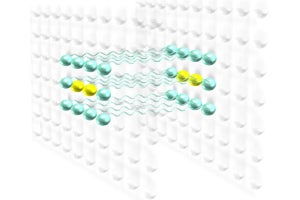

そうした中、阪大と富士通は2021年10月から開始した共同研究の一環として、エラー訂正に基づく量子計算技術の研究開発をスタート。その成果として2023年3月に発表されたのが、STARアーキテクチャ。同技術により、量子計算に欠かせない位相回転操作を効率的に実行することで、これまで提案されているFTQC(量子エラーを訂正しながら誤りなく量子計算を実行すること)アーキテクチャよりも、少ない量子ビットと短い時間で計算を実行できる可能性がもたらされたのである。

ただし、STARアーキテクチャの実用化には、以下の2つの課題があるという。

- 位相回転ゲートのエラーを訂正しない代わりに精度を高く保つ工夫をしているが限定的であり、計算可能な規模に限界があること

- 具体的な計算問題を解く際に、同アーキテクチャ自体の基本的な計算ルールである論理ゲートは明らかになっているものの、その計算問題に適した量子ビットの操作方法である物理ゲートの手順が確立されていないこと

そこで研究チームは今回、これらの課題の解決に挑むことにしたとする。

今回の研究では、まずSTARアーキテクチャでの計算規模は位相回転操作における位相角の精度で決まるため、精度が落ちないように、エラー耐性を強化した位相角の準備方法が再構築され、エラーを1000分の1に抑制する新しい位相回転技術が開発された。これにより、材料物性計算において1000倍の計算規模拡大に成功し、これまでこのアーキテクチャでは不可能だった複雑な計算、たとえば、将来的には電力インフラの送電ロス削減などにもつながる可能性のある、高温超伝導体開発のための理論モデルである「ハバードモデル」のエネルギー推定計算が可能になったという。

またSTARアーキテクチャに基づいた、量子ビットの具体的な操作手順を自動生成するシステムである「量子回路ジェネレータ」も構築された。同システムでは、量子計算の基本的な操作である論理ゲートから、実際に量子ビットを操作する物理ゲートまでを一気通貫に変換し、さらに量子ビットの操作手順を動的に変更することにより、計算時間を極限まで短くする高速化技術が搭載されている。これにより、STARアーキテクチャを使って、さまざまな計算問題を解くための具体的かつ効率的な方法が明らかにされたとした。

今回の計算規模拡大と量子回路ジェネレータの高速化技術を駆使し、STARアーキテクチャでハバードモデルを計算する際に必要となる量子ビット数と計算時間の分析が行われた。すると、6万個の量子ビットがあれば、現行コンピュータが約5年かかる8×8結晶格子ハバードモデルの計算を、わずか10時間で計算実行可能なことがわかった。これは、FTQCで現行コンピュータの計算速度を超えるのに典型的に必要とされていた100万量子ビットに比べると1桁以上小さく、2030年ころに到来が予期されるEarly-FTQC時代(数万程度の量子ビットしか実装できておらず、誤り耐性量子計算が十分に実現できないと考えられている時代)に実現可能な規模とした。

より大規模なハバードモデルの計算が解けると、他の解析手法との組み合わせで超伝導物質の電子状態のより詳細な分析が可能になり、高温超伝導体などの産業用材料の開発を加速させることが期待できるという。今後は、STARアーキテクチャの計算規模をより拡大させると共に、量子コンピュータ実機を用いた、より複雑な材料物性計算や量子化学計算、量子機械学習などの実現を目指すとしている。