imecとASMLは6月3日(欧州時間)、ASMLの本社があるオランダのフェルトホーフェンに共同で運営する「High NA EUV Lithography Lab」を開設したことを発表した。

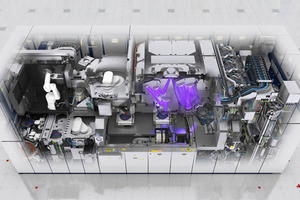

同ラボは、最先端のロジックおよびメモリメーカーならびに先端料および製造装置メーカーに、プロトタイプの高NA(NA=0.55) EUV露光装置(TWINSCAN EXE:5000)と周辺プロセス処理および計測ツールへのアクセスを提供するもので、2025年から2026年にかけて予定されている高NA EUV露光装置を用いた半導体の量産準備として重要な節目となるとしている。

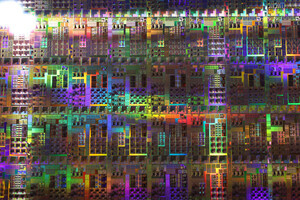

同ラボの開設に向けた整備は2018年より開始され、これまでの間にASMLとZEISSは、光源、光学系、レンズのアナモルフィック性、スティッチング、焦点深度の低減、エッジ配置エラー、オーバーレイ精度に関連する高NA EUV露光装置固有のソリューションを開発したとするほか、imecの方では、広範なサプライヤネットワークと緊密に協力して、高度なレジストと下層材料、フォトマスク、計測および検査技術、(アナモルフィック)イメージング戦略、光近接効果補正(OPC)、統合パターニングおよびエッチング技術の開発を含むパターニングエコシステムの準備が進められてきたという。これらの取り組みの結果、最近になって初めての高NA EUV露光が行われ、金属酸化物レジスト(MOR)に印刷された10nmの高密度ライン(20nmピッチ)が公開された。

-

同ラボで初めて露光に成功したウェハを手にする関係者たち。左からimec CEOのLuc Van den hove氏、ASMLの高NA EUV露光装置事業責任者のPeter Vanoppen氏、ASMLの社長兼CEOのChristophe Fouquet氏、Intel Foundry技術開発担当SVPのAnn Kelleher氏

imecの社長兼CEOであるLuc Van den hove氏は、「高NA EUVは光リソグラフィの次のマイルストーンであり、1回露光で20nmピッチのメタルライン/スペースのパターン形成が可能になり、これにより既存のマルチパターニングによるNA=0.33 EUV露光と比較して、歩留まりが向上し、サイクルタイムが短縮され、CO2排出量も削減されることとなり、ムーアの法則をオングストロームの時代まで押し進める重要な要因となる。同ラボで、プロトタイプの高NA EUV露光装置を使用して、これらの機能を実際に調査できることに興奮している。imecとそのパートナーにとって、同ラボはimecの300mmクリーンルームの仮想拡張として機能し、パターン形成エコシステムの改善を可能とする」と述べている。

なお、TWINSCAN EXE:5000の商用1号機は同ラボに先駆けて2023年末に、Intelの米オレゴン州の拠点に納入され、今年4月に組み立てを完了している。Intelは、同ラボの装置も併用していく形で、高NA EUVによる2nm以降のプロセスの量産適用1番乗りを目指す動きを見せているが、先端プロセスで先行するTSMCは、高NA EUVを急いで量産適用せずに、技術の成熟度を見極めるとしている。