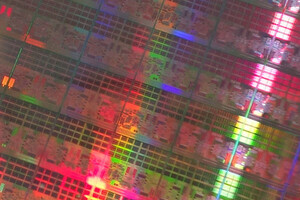

imecは、Cu対CuおよびSiCN対SiCNのダイとウェハのハイブリッド接合プロセスを、米国コロラド州デンバーで開催された「2024 IEEE Electronic Components and Technology Conference(ECTC)」にて発表した。

同プロセスでは、2μmのCuボンドパッドピッチにおいて、ダイ対ウェハオーバーレイエラーは350nm未満となり、良好な電気歩留まりを確認したとのことで、こうした微細ピッチによるダイ・ウェハ相互接続によってロジック/メモリオンロジックおよびメモリオンメモリアプリケーションへの道が開かれるとしており、将来的にはダイレベルおよびウェハレベルの光相互接続の実現にも期待できるようになるとしている。imecはECTC 2024にて、この光相互接続の概念実証を行い、0.5dB未満の光結合損失を達成したことも報告したという。

-

a)ウェハレベルの光学的に相互配線されたマルチxPUコンピューティングシステム、b)埋め込まれたSiN導波路(WG)とエバネッセントカプラを備えたPIC(フォトニック集積回路)ダイと、補完的なSiNエバネッセントカプラを備えた下部PICウェハの結合されたエバネッセントカプラで構成された実証済みのテストシステム (出所:imec)

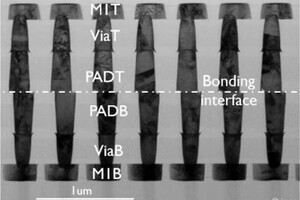

imecでは、今回の目標達成のために、ダイのシンギュレーション、ピックアンドプレース中の超クリーン表面の維持など、すべてのプロセスで高いスループットを実現。これにより、Cuボンドパッドピッチを2μmまで縮小することに成功したとする。中でもハイブリッド接合では、Cuパッドの凹みを最小限に抑えて(2.5nm未満)、表面を滑らかにするための超高品質の表面処理が重要となり、Cu/SiCN表面のCMPステップの最適化ならびに、継続して維持する必要があったとしている。また、Cu/SiCN表面へのパーティクルや衝撃のない高品質のダイ個別化を実現するために、プラズマダイシングプロセスも採用したとする。さらに、パッドピッチのスケーリングに不可欠なのは、高速でありながら高精度のピックアンドプレースステップであることから、ダイ処理と高精度のピックアンドプレースステップ技術を組み合わせることで、ダイからウェハへのオーバーレイエラーを350nm未満に保つことに成功したとするほか、アセンブリフローの最適化により、2μmピッチのCuボンドパッドにおける良好な電気的収率(Kelvin e-yieldで>85%、daisy chain e-yieldで>70%)を実現したとする。

imecのシニアフェロー R&D担当副社長 3Dシステム統合プログラムディレクターのエリック・ベイン(Eric Beyne)氏は、「ダイ・ツー・ウェハ接合は、既知の良好なダイのみを積み重ねる(結果として歩留まりが高くなる)ことと、不均一なサイズのダイを接合できるという利点があり、プロセスフローの今後の改善により、1μmの相互接続ピッチの実現も期待できる。この進化により、ダイ・ツー・ウェハ接合は、メモリ/ロジックオンロジックおよびメモリオンメモリの積み重ねの領域に入ることができるようになる」と述べている。