東北大学は4月5日、既存半導体と、自然の熱で確率的に抵抗が変化するスピントロニクス(スピン)素子をハイブリッド化することで、確率的なアルゴリズムの実行に適し、なおかつ製造容易性にも優れる"近未来版"の「確率論的(P)コンピュータ」(以下、「近未来版」と省略)を開発してその動作を検証し、スピン素子が生成する物理乱数で「疑似乱数」生成半導体回路を駆動することで、優れた計算性能が得られることを確認したと発表した。

また、多数のスピン素子で構成される"最終形態"Pコンピュータ(以下、「最終形態」と省略)では、現行の半導体回路で確率的な計算を行う場合と比べ、4桁程度の小面積化と3桁程度の省エネ化を実現できることも明らかにしたと併せて発表された。

同成果は、東北大 電気通信研究所の小林奎斗大学院生(研究当時)、同・深見俊輔教授らの国際共同研究チームによるもの。詳細は、英オンライン科学誌「Nature Communications」に掲載された。

-

今回の研究の位置付け。(上段)決定論的に動作する、既存の半導体回路からなるコンピュータ。(中段)今回の研究にて動作実証された、半導体回路と少数の確率動作スピン素子からなる近未来版Pコンピュータ。(下段)今回、性能が予測された多数のスピン素子からなる最終形態のPコンピュータ。右側に回路面積、消費電力、および製造技術の比較が示されている(出所:東北大プレスリリースPDF)

複雑なプロセスが生み出す結果の予測や、結果のもととなった原因の推定、組合わせ最適化、特徴の抽出、自然現象のシミュレーションなど、複雑性の高い計算タスクを処理するためのソフトウェア技術としては、確率的なアルゴリズムが有用だとされている。しかし、それを動作させるための現在のハードウェアは、決定論的に動作する半導体回路である。同回路は予測不能な乱数の生成を苦手としており、結果として大きな回路面積と消費エネルギーを必要としてしまっている。

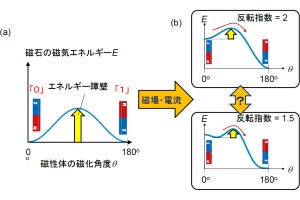

そうした中、確率的なアルゴリズムを効率的に実行できるハードとして期待されているのがPコンピュータ。同コンピュータは、短時間で0と1の信号を確率的に出力し、かつ各ビットを電気的に相関させられる情報処理の基本単位である「確率(P)ビット」を用いて演算を行う。なお、0と1の重ね合わせ状態を持ち、なおかつビット間でのもつれあい(相関状態)を形成できる量子ビットを用いる量子コンピュータとは本質的に異なるが、一定の類似性もある。またPコンピュータは比較的少ない開発コストで製造が可能とされ、現行の半導体回路の計算性能向上を可能とし、かつエネルギー効率を高めるハード技術の開発・実証が待ち望まれていたという。

そこで研究チームは今回、計算性能、小面積性(≒大規模化容易性)、エネルギー効率に優れ、なおかつ現在の半導体回路に少数のスピン素子を融合させていることから比較的容易な製造が見込まれる近未来版を開発し、その動作を実証することにしたとする。

加えて、最終形態の性能も、プロセス設計キットを用いて評価することにしたという。なお最終形態の実現には、まだ存在しない新技術をそれも複数開発する必要があるとする。しかしその実現がなれば、半導体回路の大幅な削減が可能であり、現行技術と比較した場合、トータルの回路面積と消費エネルギーを大幅に低減できるという。

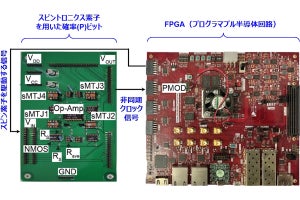

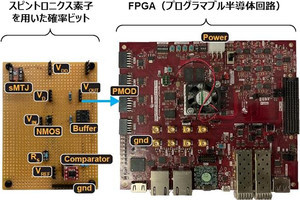

今回の研究では、プログラムで回路の書き換えが可能な半導体のFPGAと、確率動作スピン素子(超常磁性磁気トンネル接合)をケーブルで接続した簡易的な構造の近未来版のプロトタイプ実機が作製された。プロトタイプは、スピン素子からなる5つのPビットが生成する物理乱数が、FPGA内の大量の疑似乱数生成器を駆動して演算を行う設計だ。

-

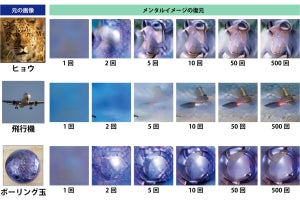

作製された近未来版Pコンピュータ(MTJ+LFSR)でサンプリングによる推定(a)と、ボルツマン機械学習(b)が行われた結果。比較対象として、一般的な乱数生成器(RNG)として知られているLFSR、および高級なRNGのXoshiroで得られた結果も示されている(出所:東北大プレスリリースPDF)

プロトタイプを用いて、確率的サンプリングによる推定と「深層ボルツマン機械学習」の性能評価が行われた。疑似乱数生成器として広く利用されている「線形帰還シフトレジスタ」(LFSR)、LFSRが出力するビット列に数学的な処理を施してそのランダム性を高めた高級な疑似乱数生成器「Xoshiro」、LFSRを確率動作スピン素子で駆動した場合の「MTJ+LFSR」が比較された。その結果、MTJ+LFSRはXoshiroと同様に計算を重ねるにつれて解の精度、および学習の効果が高まっていくことが確認されたという。つまり、高い計算性能を少ないリソースで実現できることがわかったのである。

続いて、プロセス設計キットを用いて、最終形態、LFSR、Xoshiroの、スピン素子からなる確率ビットを形成するのに必要なトランジスタ数と、1つの乱数を生成するのに必要なエネルギーの比較が行われた。その結果、最終形態のスピン素子Pビットは、同等の計算性能が実現されるXoshiro Pビットと比べ、トランジスタ数はわずかに0.0003倍、消費エネルギーもわずか0.007倍で済むことが明らかにされた。

-

プロセス設計キットを用いて評価された1つのPビットの形成に必要なトランジスタ数、および1つの乱数を生成するのに必要なエネルギー。画像3と同様に、LFSRを用いたPビット(LFSR p bit)、およびXoshiroを用いたPビット(Xoshiro p bit)の結果が、スピン素子からなるPビット(sMTJ p-bit)と共に示されている(出所:東北大プレスリリースPDF)

今後、近未来版の活用を通してその有用性を明らかにしつつ、より省エネ性と大規模化容易性に優れた最終形態の実現に向けた本格的な開発が進展することが期待されるとしている。