はじめに

A/Dコンバータ(ADC)のデータシートに掲載されている電源パラメータを理解すると、より信頼性の高い高精度データアクイジション(DAQ)システムを設計できます。特に、ADCデータシートの消費電流は、定常状態の動作条件で規定された平均値であることを理解することが重要です。したがって、ADCの過渡電流が規定のADC電流より数桁大きくなる可能性があるとしても、これらの測定電流値は過渡電流要求の特性を示すものではありません。過渡電流は、異なるADC動作モード間の遷移中に発生する可能性があり、デバイスへの最初の電力供給時に最も大きくなります。さらに、ADCを取り囲む回路と部品が原因で、さらに大きな過渡電流要求が発生する可能性があります。

本稿では、ADCの過渡電流要件について詳細に説明します。最初に、代表的なADCのデータシートが電流をどのように規定しているかを紹介し、次に、さまざまな動作条件下で過渡電流要求を定量化するいくつかのテストの結果を示します。さらに、平均電流と過渡電流の両方を供給できる複数の電源構成について説明し、最後にさまざまなパワーダウン方式が及ぼす影響を比較します。

電源の仕様

ADCのデータシートに記載されている消費電流は、定常状態の動作条件で規定された平均値です。さまざまな動作条件を持つADCでは、いくつかの電流値の仕様が必要です。これらの条件には、データレートに対してスケーリングされる平均ADC電源電流、またはプログラマブル ゲインアンプ(PGA)や電圧リファレンス(VREF)などの内部機能をイネーブルにしたときの、電流需要の増加を含めることができます。たとえば、表1にPGAとVREFを内蔵した24ビット、40kSPS、11チャネルのΔΣADCであるテキサス・インスツルメンツ(TI)の「ADS1261」の、さまざまな動作条件でのデータシート記載の電源仕様を示します。

表1で強調されている「PGAバイパス」の部分は、PGAをバイパスした通常動作時にADS1261に引き込まれる平均アナログ電流が2.7mA(標準値)または4.5mA(最大値)であることを示しています。強調されている「アナログ電源電流(機能別)」の部分は、各機能をイネーブルにしたときの電流の増加量を示しています。これらの消費電流仕様はすべて、電流が安定した後にデバイスが引き込む平均電流を測定することで規定されています。

したがって、データシートの電源仕様では、デバイスまたはサポートしている回路が通常動作時に必要とするあらゆる過渡電流の要求を平均化しています。起動時およびスイッチング時の過渡電流が、データシートに規定されている値よりも大幅に大きくなる可能性があるため、これは重要です。信頼性の高いシステム設計を実現するには、平均電流と過渡電流の両方の需要に対応できる必要があります。

過渡電流

過渡電流に関する課題の1つは、ADCの動作条件や周囲の回路により、その大きさと持続時間が大幅に変化する可能性があることです。したがって、ADCのデータシートで過渡電流が規定されていることはほとんどありません。ただし、電源パターンと直列に配置した、抵抗値が小さい抵抗の両端をオシロスコープでプロービングし、特定のシステム構成で過渡電流を測定することは可能です。その後、オームの法則を使用して、結果として生じる電流を求めることができます。

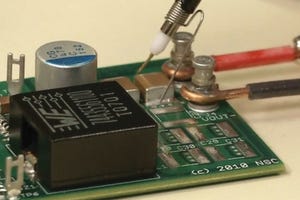

ADS1261には、電源出力とADCのAVDDピンの間にこのような抵抗が組み込まれた、評価基板(EVM)があります。10Ωの測定抵抗(R33)を含む、EVM回路図の関連部分を 図1に示します。この抵抗の両端での平均または過渡電圧降下を測定して10Ωで除算すると、ADS1261に引き込まれる平均または過渡電流がそれぞれ計算されます。このADCの過渡電流の挙動をより的確に理解できるように、さまざまな条件下で複数のテストを実施しました。

最初の過渡電流テストは、推奨される10μF(C23)と0.1μF(C24)のデカップリングコンデンサをAVDDとグランドとの間に取り付けたパワーアップテストでした。図2に、これらの条件下でのADS1261の過渡電流を示します。

表1に示したADS1261の電源仕様によれば、PGAがディセーブルされた状態での平均電流は2.7mA(標準値)または 4.5mA(最大値)となることに注意してください。ただし、図2の青い矢印はADS1261の最初の電源投入時に発生する250mAの過渡スパイクを示しています。この過渡電流は、データシートに規定されている電流の標準値の90倍超、最大電流の55倍超です。ADCの状態が変化すると、同様の電流スパイクが発生する可能性があります。

図2の緑色の矢印は、デカップリングコンデンサの充電に必要な2番目の過渡電流を示しています。通常の動作条件では、デカップリングコンデンサに追加の電荷が蓄積され、過渡事象が発生したときに追加の電流を供給します。この追加の電荷は、ADCの動作に影響を及ぼさないように、安定した電源電圧を維持するのに役立ちます。ただし、これらのコンデンサは、システムに電力が供給されるときに、未充電状態から電源電圧まで充電する必要があります。電源が供給されていないコンデンサは、システム電源がオンになった瞬間は短絡のように動作し、大きな突入電流が発生します。デカップリングコンデンサの値が大きくなると、突入電流の大きさも大きくなります。

ADCに必要な過渡電流のみを測定するため、2回目の過渡電流テストでは、図1でAVDDとグランドの間に挿入した推奨のデカップリングコンデンサ(10μFおよび0.1μF)を取り外しました。図3に、これらの条件下でのADS1261の過渡電流を示します。

図1の45mAの過渡スパイク電流は、スイッチングに起因するADC に必要なパワーアップ電流のみを表しています。予想どおり、デカップリングコンデンサを取り付けたときに発生した250mAのスパイクに比べて、ADCのみの過渡電流は小さくなっています。ただし、このように過渡振幅が小さくなると、ADCが定常状態の電流に達するまでの時間が大幅に長くなります。これは、コンデンサが補助電荷を供給しなくなるためです。また、この45mAの過渡電流は、表1に示した4.5mAの最大ADC電流仕様の10倍です。

3番目の一連のテストを実施し、さまざまな機能が過渡電流スパイクを引き起こす可能性があることも確認しました。ADS1261のVREFをイネーブルにすることは、このようなスパイクを発生させる機能の1つでした。図4に、観測されたこの過渡電流の挙動を示します。

表1から、ADS1261の標準的なVREF電流は0.2mAであることに注意してください。PGAをディセーブルにして(2.7mA)内部VREFがイネーブルの状態でADCを動作させると、合計電流2.9mAが生成されるはずです。ただし、図4で測定された60mAの過渡電流は、予想した値の20倍を超えています。この過渡電流は、概ねVREF出力ピンとグランドとの間に配置されたフィルタコンデンサを充電するために必要な突入電流に起因します。

図4の興味深い特性の1つは、基本的に過渡パルス全体にわたって、電流需要が60mAで一定に保たれることです。この挙動はADS1261の内部VREFに設計された固有の電流制限のために発生し、REFOUTピンがグランドに短絡した場合にADCを保護するのに役立ちます。

すべての動作条件をテストしたわけではありませんが、追加の機能テストをいくつか実行したところ、測定可能な過渡電流は発生しませんでした。また、この動作はADS1261に限定されないことにも注意してください。この記事で説明した過渡電流は、すべての高精度ADCで観測される可能性があります。

電源回路オプション

過渡電流は電圧ドループなどの問題を引き起こす可能性があり、ADCの動作が不安定になることがあります。したがって、平均電流と過渡電流の両方の要求に対応できる電源を設計することが重要です。以下の3つの電源オプションの利点と課題をご確認ください。

- 低ドロップアウト(LDO)レギュレータ:TIでは、高精度ADCへの電力供給にLDOを使用することを推奨します。LDOには、優れたノイズ特性、低電圧リップル、小型でシンプルな実装など、多くの利点があります。LDOの最も重要な利点は、過渡時に出力電圧を確実に維持できると同時に、低い静止電流を実現できることです。

- リニアレギュレータ:LDO ではコストが高すぎる場合、標準ドロップアウト電圧のリニアレギュレータも良い選択肢となります。リニアレギュレータは過渡時に出力電圧を確実に維持できると同時に、LDOと同様に低い静止電流を実現します。リニアレギュレータの課題はドロップアウト電圧が大幅に高くなることで、このデバイスに電力を供給するためだけに特別の電圧レールが必要になる場合があります。また、リニアレギュレータは効率が低く、放熱量が大きいため、大型のパッケージになる傾向があります。より多くの熱が発生すると、閉じたシステムの温度が上昇する可能性があり、高精度システムのドリフト誤差につながる可能性があります。

- シャントレギュレータ:最もコスト効率の高い電源オプションの1つは、シャントレギュレータです。コストを削減できる一方、信頼性の高い電源回路が必要になり設計がより複雑になります。たとえば、バイポーラ電源動作を必要とする高精度ADCでは、低電圧の可変シャントレギュレータである「TLV431」を使用して±2.5Vレールを生成する場合があります。TLV431はVREFが小さいのでこの目的で使用できます。ただし、このレギュレータの課題の1つは、供給できる電流量が限られていることです。TLV431のデータシートによると、1mA以上のカソード電流も必要です。これら2つの制約により、図5および図6に示す標準設定の出力電流能力が制限されます。

図5と図6は、カソード電流とADCに供給される電流の両方が抵抗R1を流れる必要があることを示しています。この構成では、電源電流が(VSUP - VREF)/R1に制限されるため、2つの設計上の課題が発生します。第1に、R1を連続的に流れる電流は、負荷が印加されていない場合でも電力を消費することです。R1を小さくして利用可能な電源電流を増加させようとすると、それに比例して静的電力散逸も増加します。第2に、R1で設定される最大電流は通常、ADCが必要とする数百ミリアンペアの過渡電流をサポートできないことです。必要な電流を供給できないと、電源電圧が低下し、ADCの動作が不安定になる可能性があります。

図5と図6の回路に 2つの部品を追加することで、これらの問題を軽減します。図7と図8に、トランジスタとバイアス抵抗Rbを含む変更後のシャントレギュレータ回路を示します。

図7および図8の電源回路は、図5および図6のシステムよりも多くの電流を供給できます。これは、トランジスタによって電源入力(VSUP)と出力(VOUT)の間のあらゆる抵抗が除去されるためです。この新しい回路は、R1に依存する代わりにRbを取り付けることで、1mA以上のカソード電流を維持することもできます。したがって、抵抗R1およびR2は、式1にしたがって出力電圧を設定する場合にのみ必要です。

低消費電力システム:パワー ダウンかパワー オフか?

低消費電力DAQシステムは、さまざまなパワーダウン方式を使用してエネルギーを節約することがよくあります。一部のADCにはパワーダウンモードがあり、デバイスを使用していないときにデバイスを低消費電力状態に移行させ、システムの消費電力を低減することができます。ADCデータシートにはさらに、このモードでの消費電流が規定されています。もう1つのよく使われる省電力手法は、ADCを使用していないときに電源を単純にオフにし、必要なときに電源をオンに戻す方法です。この方法では、システムの電源がオフの間は消費電力が発生しません。

後者の方法は、この記事で説明する過渡電流の影響を受けますが、これは電源サイクルのたびにあらゆるコンデンサを再充電する必要があるためです。電荷(Q)と電流(I)の標準的な式を使用して、電源がオフになったときにシステムが消費する電流を推定し、この値をパワーダウンモードのADCデータシートの値と比較することができます。

たとえば、ADS1261のデータシートでは、10μFおよび0.1μFのデカップリングコンデンサをAVDDからAVSSまでの間に並列に接続することを推奨しています。また、データシートにはAVDDが5Vでなくてはならない、と規定しています。式2と式3により電源サイクルが毎秒1回の場合、平均電流が50.5μAであると計算されます。

ここで、C=10.1μF(10μF+0.1μF)、V=5V、t=1sです。

表1の緑色で強調表示されている部分では、パワーダウンモードでのADS1261のパワーダウン電流は8μA(最大)であることに注意してください。両方のオプションを比較すると、ADCのパワーダウンモードを使用することで、電源をオフにする場合に比べて消費電力を6倍以上低減できることがわかります。したがって、過渡電流が全体的な消費電力に及ぼす影響を考慮することが重要です。多くの場合、ADCをパワーダウン状態にすることは、エネルギー効率の優れたソリューションになります。

本記事はTIが四半期ごとに発行している技術ジャーナル「Analog Design Journal 2023年第2四半期号」に掲載した技術記事を翻訳したものとなります。

参考文献

・e-book(英語):LDOの基礎

・e-book(英語):電圧リファレンスを使用した設計のヒントとコツ

・TI E2E 設計サポートフォーラム技術資料(英語):LDOまたはスイッチングレギュレータを選択する方法

・TI E2E 設計サポートフォーラム技術資料(英語):電圧リファレンスを電圧レギュレータとして使用する方法

・アプリケーションレポート(英語):TL431およびTL432 データシートの安定性境界条件チャートについて

著者プロフィール

Luke AllenTexas Instruments

Applications Engineer

Bryan Lizon

Texas Instruments

Applications Manager