概要

データ・コンバータ(A/Dコンバータ、D/Aコンバータ)の高速化を求める声は絶えることがありません。その結果、現在では超広帯域のダイレクトRFサンプリングに対応するものも製品化されています。そうした製品では、「JESD204BまたはJESD204C」(以下、JESD204B/C)に対応するインタフェースがよく使われています。本稿では、より高速なデータ転送を可能にするJESD204B/Cに対応したインタフェース(以下、JESD204B/Cインタフェース)の実装方法について解説します。それに向けて、まずJESD204B/Cインタフェースを備える高速データ・コンバータは、最終的なシステム・アプリケーションにどのような付加価値をもたらすのかを明らかにします。続いて、各実装レイヤ(層)の役割について説明します。また、シームレスなアップグレードを可能にするFPGA用のIP(Intellectual Property)、ツール、プラットフォーム・ソリューションを紹介します。更に、インタフェースを実装した後、最適なアプローチでデバッグを実施するための手法について解説を加えます。

高速データ・コンバータ用のインタフェース

データ・コンバータ製品は、より速いサンプル・レートとより高い分解能をサポートすべく進化を続けています。その過程では、データ転送速度がより高まることに依存し、シグナル・インテグリティに関する問題が顕在化してきました。言い換えれば、旧来の入出力(I/O)技術では、帯域幅の拡大に伴う今日の要件を満たせないということです。

高速データ・コンバータ製品には、消費電力の面で最適化されたDSPエンジンが組み込まれるようになりました。つまり、データ・コンバータがより多くのシステム負荷を負担するようになったということです。実際、受信パスには、高度な構成(コンフィギュレーション)が可能なデジタル・ダウンコンバータ(DDC:Digital Downconverter)や、プログラムが可能なFIR(Finite Impulse Response:有限インパルス応答)フィルタ、自動利得制御(AGC:Automatic Gain Control)などの機能が設けられます。一方、送信パスには、デジタル・アップコンバータ(DUC:Digital Upconverter)、プログラマブルな遅延回路、デジタル・プリディストーション(DPD:Digital Predistortion)機能などが実装されます。これらの機能は、FPGAやASICからデータ・コンバータへのオフロードを可能にします。その結果、より広い帯域幅に対応可能なシステムや、優れたSWaP(サイズ、重量、消費電力)を実現できるようになります。

JESD204B/Cの規格は、次世代のデータ・コンバータを使用するアプリケーションの要求を満たすように設計されています。そのインタフェースは、広帯域幅のSerDes(Serializer/ Deserializer)をベースとしています。また、プロトコル・レベルのエンコーディング、スクランブリング、同期技術が活用されています。差動方式の相互接続の数を減らしつつ、最高32.5Gbpsの転送速度を実現できることを大きな特徴とします。

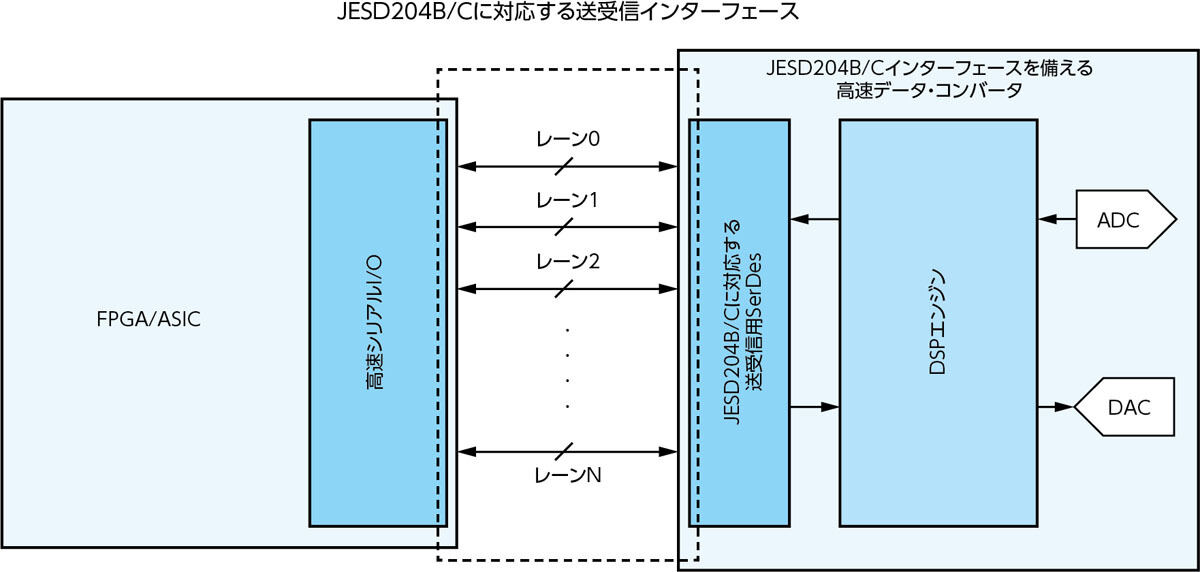

図1は、高速データ・コンバータとFPGAの間の典型的なインタフェースを表したものです。例えば、アナログ・デバイセズが提供する「MxFEファミリ」の最新製品も、この種のインタフェースを採用しています。JESD204B/Cインタフェースは、送信用と受信用にそれぞれ最大24系統の差動並列レーンをサポートします。送信側、受信側のそれぞれが最高32.5Gbpsのデータ転送に対応するので、各方向で同時にほぼ800Gbpsの正味のスループットが得られます。

FPGAにおけるJESD204B/Cインタフェースの実装方法

実際のアプリケーションでは、A/Dコンバータ(ADC)、D/Aコンバータ(DAC)、またはMxFEとFPGAの間で使用するJESD204B/Cインタフェースを実装することになります。そのインタフェースを介したデータの流れは、JESD204B、JESD204Cのうちいずれかの規格によって規定されたとおりになります。

JESD204Bでは、システム内のトランスミッタがパラレル・データをフレームとしてアセンブルします。その際には、8b/10bエンコーディングとオプションのスクランブリングを使用してシリアルの出力データが形成されます。最初にリンクを確立する際には、同期をとるための特別な制御文字(キャラクタ)を送受信する必要があります。また、同期を維持するために、データ・ストリームには追加のキャラクタが埋め込まれます。

JESD204Bのプロトコルでは、レーン・レートが16Gbpsに制限されています。一方、JESD204Cのプロトコルは最高32.75Gbpsのレーン・レートをサポートしています。JESD204Cは64b/66bエンコーディングを採用しているので、エンコーディングの効率が大幅に向上しています。また、完全にフィードフォワードの同期プロセスを採用しているので、最初にリンクを確立する際、同期を得るためのハンドシェイクのプロセスは必要ありません。

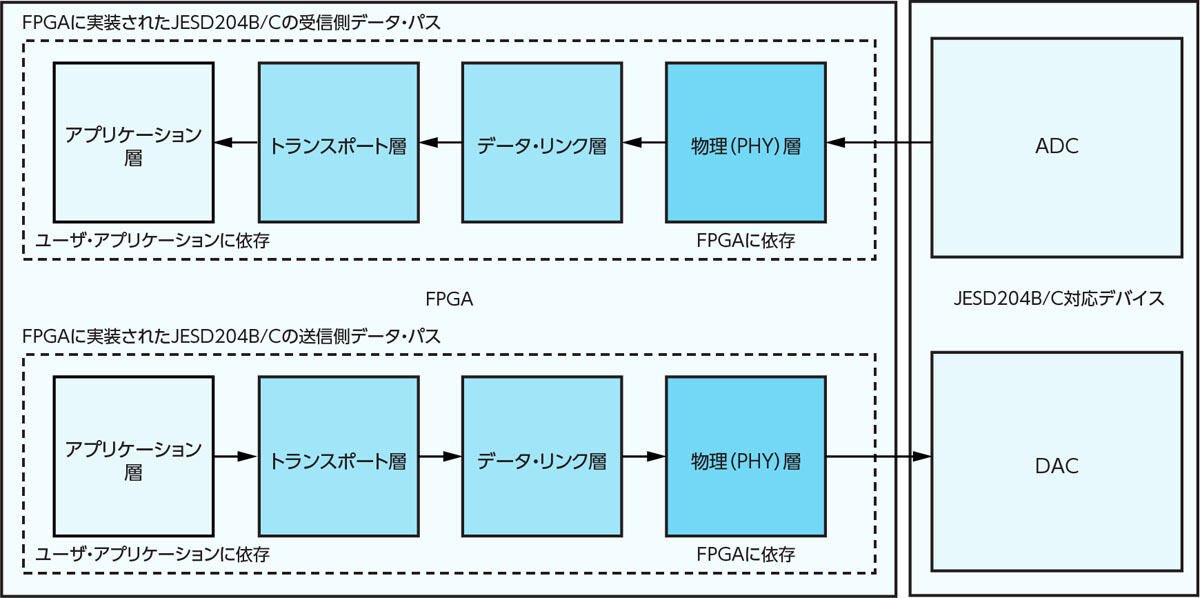

図2は、JESD204B/Cのデータ・パスを4つの層に大別して示したものです。各層は特定のタスクを実行するように設計されます。

JESD204B/Cに対応するFPGA用のIP

アナログ・デバイセズやFPGAベンダーは、JESD204B/Cのデータ・パスの各層に対応するIP(FPGA上に実装)を提供しています。その目的は、JESD204B/Cインタフェースを備える高速データ・コンバータ製品と接続するシステムの開発を加速できるようにすることです。最終的にどのような選択をするのかは、システムに関連するソフトウェア/ハードウェアに応じて決まります。ただ、FPGA用のIPモジュールは十分な柔軟性を備える形で構築されています。そのため、できるだけ最良のソリューションを実現するために様々なアプローチを採用することができます。

以下、図2に示した各層について説明します。

物理層

物理(PHY)層では、SerDesを使用することにより、指定されたライン・レートでプロトコルのフレームを伝送します。SerDesには、送信用ドライバ、受信用イコライザ、クロック・データ・リカバリ(CDR:Clock Data Recovery)回路が含まれています。

多くの場合、物理層はハードウェア化されたトランシーバーのIPを必要とし、FPGAに依存することになります。つまり、使用できるものはFPGAベンダーやFPGAの製品ファミリによって異なるということです。Xilinxを買収したAMD(Advanced Micro Devices)は、高速シリアル・トランシーバーとして「GTX」、「GTH」、「GTY」、「GTY-P」の各シリーズを提供しています。これらは、同社のFPGAで利用可能なオプションです。同様に、Intelのトランシーバー用PHY製品である「L-Tile」、「H-Tile」、「E-Tile」のシリーズは、同社のFPGA用のオプションとして使用できます。各トランシーバーは最大定格値が異なります。その値は、各FPGAが最終的なアプリケーションに適しているか否かを判断する上で不可欠な指標になります。

データ・リンク層

データ・リンク層は、選択したプロトコルに基づいて8b/10bまたは64b/66bのエンコーディング/デコーディングを実行します。また、デスクランブル、レーンのアライメント、レーンのデータのデフレームを実施します。加えて、JESD204Bでは、フレーム・アライメント・キャラクタの置換が行われます。一方、JESD204Cでは、リンク上のデータの同期に必要なマルチブロックおよび拡張マルチブロックのアライメントが実行されます。

アナログ・デバイセズも、JESD204B/Cに対応する送信側のデータ・リンク層のIPと受信側のデータ・リンク層のIPを提供しています。それらのIPは、アナログ・デバイセズの高速データ・コンバータ製品との相互運用性を考慮して最適化されています。各データ・コンバータとFPGAをつなぐインタフェースを設計する際には、暗号化されていないRTLのコードとIP用のドライバを利用できます。

データ・リンク層では、AMDのFPGAまたはIntelのFPGA向けのJESD204対応フレーマーIP/デフレーマーIPも使用可能です。

トランスポート層

送信パスのトランスポート層は、レーンのデータをADCのサンプル・データに戻す役割を果たします。一方、受信パスのトランスポート層はDACのパターン・データをレーンのデータに変換します。サンプル・データのフォーマットは構成(コンフィギュレーション)によって決定されます。

アナログ・デバイセズは、ADC用のコンパニオン・トランスポート層RTLコード・ジェネレータとDAC用のコンパニオン・トランスポート層RTLコード・ジェネレータを提供しています。これらはスクリプト・ベースのツールであり、JESD204B/C のモードの入力リストに基づいてトランスポート層のデータを生成します。いずれも、高速データ・コンバータ製品によって提供可能なすべてのモードをサポートしています。

コンパイルを実施する際、設計において単一のモード・セットのサポートだけが必要な場合には、「ADC JESD204B/C Transport Peripheral」と「DAC JESD204B/C Transport Peripheral」を使用することができます。

アプリケーション層

アプリケーション層では、データに対する様々な前処理や後処理を実施します。その目的は、特定の機能セットの実行や最終アプリケーションにおけるより効率的なデータ処理を円滑に行えるようにすることです。

ほとんどの場合、アプリケーション層のコードは個々のアプリケーションに固有のものになります。ただ、アナログ・デバイセズは、特定の高度なユース・ケースをサポートするFPGA用のIPを用意しています。それらは、お客様のご要望に応じて提供されます。

リファレンス設計の活用

上述したFPGA用のIPは、FPGAベースのリファレンス設計の一部として使用できます。あるいは、アナログ・デバイセズの高速データ・コンバータ製品を使用するカスタムの設計においてスタンドアロンのIPモジュールとして使用することも可能です。それらのリファレンス設計は、アナログ・デバイセズの様々なFPGA用カスタム・プラットフォームやCOTS(商用オフザシェルフ)のFPGA用プラットフォームでサポートされています。

お客様がシステムの構築に向けて製品を統合する際には、高速ADC/DACやMxFE製品ファミリの機能、性能をどれだけ適切に評価できるのかが非常に重要になります。高速データ・コンバータの評価用ボードは、FPGAをベースとするデータ・コントローラ・ボードとのインタフェースを備えています。それにより、ADCからサンプルを取得したり、DACにサンプルを受け渡したりすることができます。

アナログ・デバイセズの高速データ・コンバータ製品の場合、JESD204B/Cのデータ用インタフェースとその他のI/O制御用インタフェースは、多ピン・コネクタの規格であるVITA 57.4を活用してFMCコネクタまたはFMC+コネクタにルーティングされます。また、ハードウェア・コンポーネントは、FPGAとソフトウェア・ソリューションのオプションによってサポートされています。そのため、お客様は導入が容易だというメリットを享受できます。

アナログ・デバイセズのFPGA用プラットフォーム

アナログ・デバイセズは、FPGAに対応する各種の評価用プラットフォームを提供しています。「ADS7-V2EBZ」、「ADS8-V1EBZ」、「ADS8-V3EBZ」、「ADS9-V2EBZ」の他、リリース途上の「ADS10-V1EBZ」があります。これらのプラットフォームは、製品の評価や、お客様の最終アプリケーションの概念実証に向けた設計/実装に適しています。

図3は、MxFEファミリの製品とのインタフェースとしてFPGA対応の評価用ボードであるADS9-V2EBZを使用する例です。このボードでは、AMDの「Kintex UltraScale+ FPGA」を使用しています。同FPGAは、1つのFMC+コネクタに接続された28Gbps対応の20個のトランシーバーをサポートします。HMC(Hybrid Memory Cube)ベースのDRAMモジュールは、高いデータ・スループットを提供します。それ以外にも、電力分配ネットワークや、デタミニスティックなリンクの遅延をサポートすることができるスケーラブルなクロック生成アーキテクチャなどを備えています。

各データ・コンバータ製品のページには、その製品に適したFPGA対応の評価用ボードのページへのリンクが設けられています。また、FPGA用のバイナリ・ファイルやソフトウェア・スイートの情報も入手できます。FPGA用のソース・コードには、JESD204B/Cのデータ・パスのマルチモードをサポートするRTLのコードが含まれています。それらのコードは、高い構成可能性を備えています。また、メモリ・コントローラ、Embedded C用のドライバ、リンクの確立/データ・フローの制御を担うステート・マシン用のRTLコードも提供されています。JESD204B/Cインタフェースを備える高速データ・コンバータの採用に向けてFPGA用のソース・コードが必要になった場合には、アナログ・デバイセズに直接リクエストしてください。

COTSのFPGA用プラットフォーム

ここで言うCOTSのFPGA用プラットフォームとは、AMDやIntelが提供しているFPGA対応ボードのことです。それらを採用すれば、希望のライン・レートとメモリ帯域幅の要件を満たすと共に、十分な量のロジックとI/Oリソースを活用できるでしょう。アナログ・デバイセズは、それらと相互運用性を持つボードのサブセットをリファレンス設計として提供しています。それらは、製品の評価や概念実証用の設計/実装に役立ちます。各リファレンス設計には、アナログ・デバイセズが提供するJESD204B/C対応のIPやドライバに加え、イーサネットを介して各ボードとデータをやり取りするためのソフトウェア・スタックが含まれています。

FPGA用のリファレンスのコードや、ドライバや詳細なドキュメントを含むソフトウェア・インフラは、アナログ・デバイセズのWikiページからサンプル・プロジェクトとしてダウンロードすることができます。

アナログ・デバイセズのJESD204B/C対応ツール

FPGA用のIPや評価用ボードに加え、アナログ・デバイセズはJESD204B/Cインタフェースの実装を容易に行えるようにするための様々な開発ツールを用意しています。以下、それらのうちいくつかを紹介します。

IBIS-AMIモデル

IBIS-AMI(Algorithmic Modeling Interface)モデルを使用すれば、シリアライザとデシリアライザの高速リンクのモデリングを実施できます。そのモデルには、トランスミッタ/レシーバーにおけるイコライゼーション用のアルゴリズムを含めることも可能です。アナログ・デバイセズの高速データ・コンバータの製品ページには、使用するSerDesの物理層用IPに基づくIBIS-AMIモデルのリストが掲載されています。

モード選択用のツール

JESD204B/JESD204C Mode Selector Toolは、コマンド・ラインをベースとするツールです。これを使用すれば、特定の最終アプリケーションのユース・ケースに対応するために必要なモードの数を絞り込むことができます。その際には、ユース・ケースについて説明するフロー・チャートを通じ、ユーザに対してガイドが提供されます。それにより、システムの設計に関連する送受信モードを特定することが可能になります。

フレームのマッピング・テーブルの生成

JESD204x Frame Mapping Table Generatorを使用すれば、データ・コンバータのサンプルの配置方法を容易に理解することができます。同ツールには、JESD204B/Cのパラメータ(L、M、F、S、NP)の有効な組み合わせを入力します。すると、そのモードにおけるフレームのマッピング情報が表形式でファイルに出力されます。

JESD204B/Cインタフェースのデバッグ

アナログ・デバイセズの高速データ・コンバータは、デバッグ用のレジスタ・フィールドとテスト・モードを備えています。また、各プロトコル層のIPブロックには、JESD204B/Cインタフェースをシステムに実装した後、デバッグ作業を支援するために有効にできる機能が用意されています。以下、デバッグ用の各種機能などについて説明していきます。

物理層のデバッグ

高速データ・コンバータとFPGAの間の物理インタフェースは、高速の信号を扱います。高速な立ち上がりエッジと立下がりエッジを伴うそれらの信号は、ボード上のパラレル・レーンによって伝送されます。JESD204B/Cのリンクのデバッグを行う際、物理層については次に説明する2つの事柄に注目するとよいでしょう。

SerDesのクロッキング

高速データ・コンバータとFPGAは、シリアルの送受信パスを駆動するための高速クロックを必要とします。通常、そのクロックは、フェーズ・ロック・ループ(PLL)シンセサイザによって生成します。PLLはCDR回路の重要なブロックであり、通常はライン・レートとの関係が定義されたリファレンス・クロックを使って動作します。アナログ・デバイセズのデータ・コンバータとFPGA用のIPには、PLLのロックを確認する機能が用意されています。リファレンス・クロックが正しいレートに設定されていない場合、PLLはロックしません。

PRBSパターン

データ・コンバータとFPGAの間では、高速パラレル・レーンを介して様々なデータがやり取りされます。その結果、データ・パターンに対して何らかの影響が及ぶ可能性があります。とり得るすべてのデータ・パターンに及ぶ影響についてテストするためには、PRBS(Pseudo Random Binary Sequence)パターンが使用されます。PRBSパターンは、物理インタフェースのシグナル・インテグリティのテストを行う上でも有用なツールです。アナログ・デバイセズのADC、DAC、MxFEファミリ製品は、PRBSモード(PRBS7、PRBS15、PRBS31)をサポートしています。それらのパターンは、各製品がサポートする最大レートで使用できます。

先述したように、AMDとIntelはトランシーバー向けに物理層用のIPを提供しています。それらも、PRBSパターンに対応するモードを内蔵しています。また、シグナル・インテグリティのテスト向けに、スタンドアロンで使用可能なIPブロック(Xilinx iBERTとして知られるものなど)も用意されています。それらのIPは、プリエンファシス機能、ポストエンファシス機能、電圧振幅の設定機能などを備えています。そうした機能を利用することで、シグナル・インテグリティの問題に対応するための調整を行うことができます。

データ・リンク層のデバッグ

JESD204B/Cのリンクを確立するプロセスには同期シーケンスが含まれています。これが正しく完了しないと、リンクで障害が発生します。JESD204Bのユース・ケースに対応する設計では、リンクが確実に確立されるようにしなければなりません。そのためには、コード・グループ同期(CGS:Code Group Synchronization)、イニシャル・レーン・アライメント・シーケンス(ILAS:Initial Lane Alignment Sequence)、物理同期信号を監視する必要があります。一方、JESD204Cについては、サンプル・ヘッダ(SH:Sample Header)のロックと拡張マルチブロック(EMB:Extended Multiblock)のロックについて確認しなければなりません。デバッグを行う際、データ・リンク層については、次に説明する2つの事柄に注目するとよいでしょう。

JESD204B/Cのモードのミスマッチ

インタフェースを介して送信されるデータをリンク層がどのようにエンコーディング/デコーディングするのかは、選択されたモード(L、M、F、S、K)とその他のパラメータによって決まります。そのため、データ・コンバータとFPGAは同じモードに設定しなければなりません。物理リンクからのデータ以外のデータに不一致がある場合には、JESD204B/Cのパラメータが正しく設定されているか否かを確認するとよいでしょう。

レーンのマッピングの誤り

データ・コンバータとFPGAの間には、高速信号を扱う物理パラレル・レーンが存在することになります。それらのルーティング(配線の引き回し)は、恐らく容易ではないでしょう。この制約は、レシーバーにおいて物理レーンを論理レーンにルーティングし、トランスミッタにおいて論理レーンを物理レーンにルーティングできるクロスバーを使用することで緩和できます。クロスバーを使用した結果、リンクが確立しないケースがあったとしたら、レーンのマッピングに誤りがあるのかもしれません。したがって、マッピングの確認を行うことが実用的なデバッグ作業になります。

トランスポート層のデバッグ

トランスポート層は、レーンのデータとサンプル・データの間の変換を行う役割を担います。トランスポート層から出力されるデータに不整合がある場合に推奨されるデバッグ手法があります。それはパターン・モードを利用するというものです。

アナログ・デバイセズのADCは、事前に定義された数種類のデジタル・パターンとユーザが定義したパターンを生成できるテスト・モードを内蔵しています。それらのパターンを使用すれば、簡単に出力を解釈できます。そのため、FPGAの受信側トランスポート層のエラーを検出するのが容易になります。

通常、FPGAの送信側トランスポート層は、サンプル・データを基に適切なレーン・データを生成する役割を担います。この場合、既知のパターンを入力として使用することが有効なデバッグ手法となります。

エラーの監視

当然のことながら、リンクが確立された後もデバッグの対象になります。高速データ・コンバータとFPGA用のIPモジュールは、データの送受信中にリンク上でエラーが発生すると、そのことをレポートとして通知する機能を備えています。これはリンクの監視において有用です。このことを知っていれば、システムのデバッグをより円滑に進められます。

まとめ

広帯域に対応するトランスミッタ/レシーバーは、サンプル・レートとスループットに対する要求に応えるために進化を続けています。それを受けて、アナログ・デバイセズは、最高32.75Gbpsに対応するJESD204B/Cインタフェースを備えた高速ADC/DAC、MxFE製品ファミリを提供しています。広帯域対応のRFシステムを構築する場合、それらの製品は非常に有用なものとなります。また、FPGA対応のリファレンス設計や、FPGA用のIPモジュール、最先端のツール、サポートなど、豊富な設計リソースもすぐに利用できる状態にあります。それらを活用すれば、開発時間を節約しつつ、JESD204B/Cインタフェースを備える高速データ・コンバータへのアップグレードをシームレスに実現することができます。

JESD204BまたはJESD204Cのプロトコルについてより深く理解したい方には、「JESD204Bサバイバル・ガイド」または「JESD204C入門 -- この新規格によって何が変わるのか?」を一読することをお勧めします。

JESD204や、アナログ・デバイセズの製品におけるその実装については、「JESD204とは -- データ・コンバータのシリアル・インタフェース標準規格JESD204」を参照するとよいでしょう。アナログ・デバイセズの高速コンバータについては、「RFコンバータ:マルチギガ・ヘルツ処理のイノベーション」をご参照ください。

本記事はAnalog Devicesの技術解説記事「Unlock Higher Data Transfer Speeds by Upgrading to the JESD204B/JESD204C Interface」を邦訳・改編したものとなります

著者プロフィール

Nikhil AhujaAnalog Devices(ADI)

プロダクト・アプリケーション・エンジニア

2016年に入社。ノースカロライナ州を拠点とするアドバンスド・データ・コンバータ・システム・グループに所属。システムにアナログ・デバイセズの高速データ・コンバータやMxFE製品ファミリを統合できるよう顧客支援を行っている。インドのノースキャップ大学で電気工学の学士号、ノースカロライナ州立大学でコンピュータ工学の修士号を取得