英Armは11月23日、Cortex-Mファミリーの新製品として「Cortex-M52」を発表した。これに関して日本法人であるアームより事前説明があったので、この内容をお届けしたい。

今回発表された「Cortex-M52」であるが、製品ポジションを筆者なりにまとめたのが図1である。

ラフに言えばCortex-Mの初代がArm v7-Mを搭載するCortex-M0/M0+/M3/M4/M7のラインナップで、これがCortex-Mシリーズの基本となる。次に、そのArm v7-MにTrustZoneの実装を追加したのがArm v8-Mで、これはCortex-M23とM33/M35Pの3製品が用意される。Cortex-M35Pはちょっと聞き慣れないが、Cortex-M33にAnti-Tamper性を持たせたSecure Processorであり、2018年に発表されている。最後がCortex-M55/M85と今回発表のM52で、これは2020年に発表されたArm v8.1-Mを実装した製品群となる。このArm v8.1-Mはいくつか特徴があるが、一番大きなものはMVE(M-profile Vector Extension)に対応、具体的にはHeliumの実装が行われたものとなる。

ようするにCortex-M3/M4などメインストリーム向けのMCUにもSIMDエンジンが搭載されることになったという訳だ。Cortex-M52は、DSP Extensionでは従来比2.7倍、ML Performanceで5.6倍の処理性能を持ち、EdgeというかEndpoint DeviceでのML処理を大幅に高速化した、としている(Photo01)。

この性能向上は最初に書いた通りHeliumの搭載による部分が大きいのだが、そもそも何故Heliumをメインストリーム向けデバイスに搭載したか? というと、昨今このクラスでDSPを使ってMLを実装するケースが増えており(後でリストも出てくる)、こうした用途向けに抜本的に性能を引き上げる必要がある、というニーズに対応したものである。

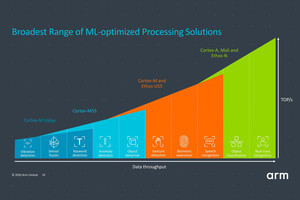

具体的なターゲットがこちら(Photo02)。

-

Photo02:以前Ethosの発表があった際にも似たようなスライドが示されているが、これと用途を見比べてみると面白い

要するにAI/MLを利用したAIoTのローエンドを担う役割がCortex-M52には期待されている事になる。

具体的な内部構造がこちら(Photo03)。

Single IssueのProcessor PipelineはCortex-M3/M4/M33などと共通であり、細かく改善はなされているそうだが、基本的にはCortex-M33と大きくは変わらない(というか、Cortex-M55と変わらない、というべきか)。差は主にHeliumユニットになるが、このHeliumがオプションではなく標準搭載、というのがCortex-M33と異なる最大のポイントかもしれない。

細かいところでは、Cortex-M55の構成図を見ると、Peripheral BusはAHBをサポートしているが、Memoryなどを接続するProcessor Busの方はAXI-5 Masterのみである。これに対してCortex-M52ではAHB-5での接続も可能になっている。これはざっくり、Heliumの要求する帯域がCortex-M55の半分であることに起因する。

以前、こちらで説明したが、Heliumそのものは128bit幅のSIMDであり、一方エンジンは32bit単位である。で、1cycleにどれだけの32bitエンジンを同時に動かせるかを「Beat」と呼ぶ。

Cortex-M55では2 Beat、つまり1cycleに32bit×2の処理が可能なので、Heliumの128bit幅のSIMDの演算には2cycle必要である。対してCortex-M52は1 Beat、つまりSIMDの演算に4cycle必要となる。なのでHeliumのスループットはCortex-M52と比べて半分となるが、その代わり必要となるメモリ帯域もCortex-M55の半分で済む。これがAXI-5に加えてAHB-5もサポート可能になった理由と思われる。

この1 BeatのHeliumユニットだが、Cortex-M3/M4/M33までと異なり、Cortex-M52ではHeliumユニットが標準搭載となった。なのでDSP拡張もHeliumの中に実装される形になっているとする。それとArm v8.1-MからはFPUでFP16をサポートする(HeliumではFPはサポートされない)。このため浮動小数点演算を使う様なケースでは、FP16を利用する事で2倍、AI/ML系ではINT 8をHeliumで実行する事により4倍の処理性能が実現するが、これに加えて細かく改良(CPUコアの側もこの1 BeatのHeliumの実装に最適化したとしている)したことで、さらに性能が改善してそれぞれ2.7倍/5.6倍という性能になったという訳だ。

このHeliumを利用する事によるデメリットはエリアサイズの増大である。Cortex-M55を基準にすると、Cortex-M52はエリアサイズが23%減、Cortex-M33は30%減とされる(Photo04)ので、つまりCortex-M33と比較した場合1割程度エリアサイズが増える計算になる。

-

Photo04:Cortex-M55と比較すると、1 BeatなのでSIMDエンジンそのものの面積は半減、またLoad/Storeユニットも64bitのRead/Writeから32bitのRead/Writeになり、という事は内部バスもそれだけ幅が狭くて行ける(CPU Pipeline用のものと同じ幅で済む)というあたりが23%もエリアサイズを削減できた理由だろう

あとは性能増がこの1割のエリアサイズ増と見合うかどうか、という事になるだろう。まぁ32bitのエンジンを1つ追加し、Helium用に128bitレジスタをいくつか追加するだけだから、1割の増加は妥当な数字だろう。

ソフトウェア的には従来のCortex-M33/M55などと共通(DSP周りの実装の違いは、ユーザーからは見えない)ので、すでに多くのエコシステムパートナーが提供するソフトウェアソリューションはそのままCortex-M52で利用可能とされる(Photo05)。

-

Photo05:主要なパートナー企業。AI/MLで言えば、例えば最近はAI/ML Solution VendorになったETA Computeの「Aptos」などもそのままCortex-M52上で動きそうだ

想定しているCenter Processは22nmとの事。すでにIPのライセンス供与はスタートしているとの事である。