Intelは9月19日~20日(米国時間)にかけて年次イベント「Intel Innovation 2023」を開催。19日に行われた基調講演にて、同社CEOのPat Gelsinger氏が次世代のノートPC向けCPU「Meteor Lake」(開発コードネーム)および「第5世代Intel Xeon スケーラブル・プロセッサ(SP)」を12月14日より正式に発売することを明らかにした。

同社はMeteor Lake世代からCPUのリブランドを実施。「Intel Core Ultra Processor」として提供され、NPU(ニューラル・プロセッサ・ユニット)の統合により、PC上で電力効率の高いAIアクセラレーションとローカルでの推論を実現するとしている。Gelsinger氏も、「AIもよりパーソナルなものになろうとしている。AIはPCの体験を根本的に変革、再構築し、クラウドとPCの連携を通じて個人の生産性と創造性を解き放つだろう。私たちはAI PCの新時代を迎えようとしている」と「AI PC」というキーワードを強調していた。

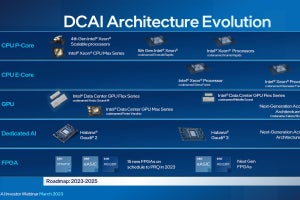

一方のXeon関連としては、第5世代Intel Xeon SP(開発コードネーム:Emerald Rapids)に加え、2024年には電力効率に優れるE(Efficient)コアを活用した最大144コア搭載の「Sierra Forest」(開発コードネーム)を2024年前半に提供を開始する予定であるとしているほか、性能重視のPコアを活用した「Granite Rapids(開発コードネーム)」、Sierra Forrestの後継となる「Clearwater Forest」(開発コードネーム)も「Birch Streamプラットフォーム」で提供されることも示された。

-

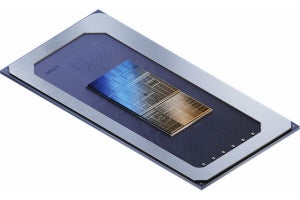

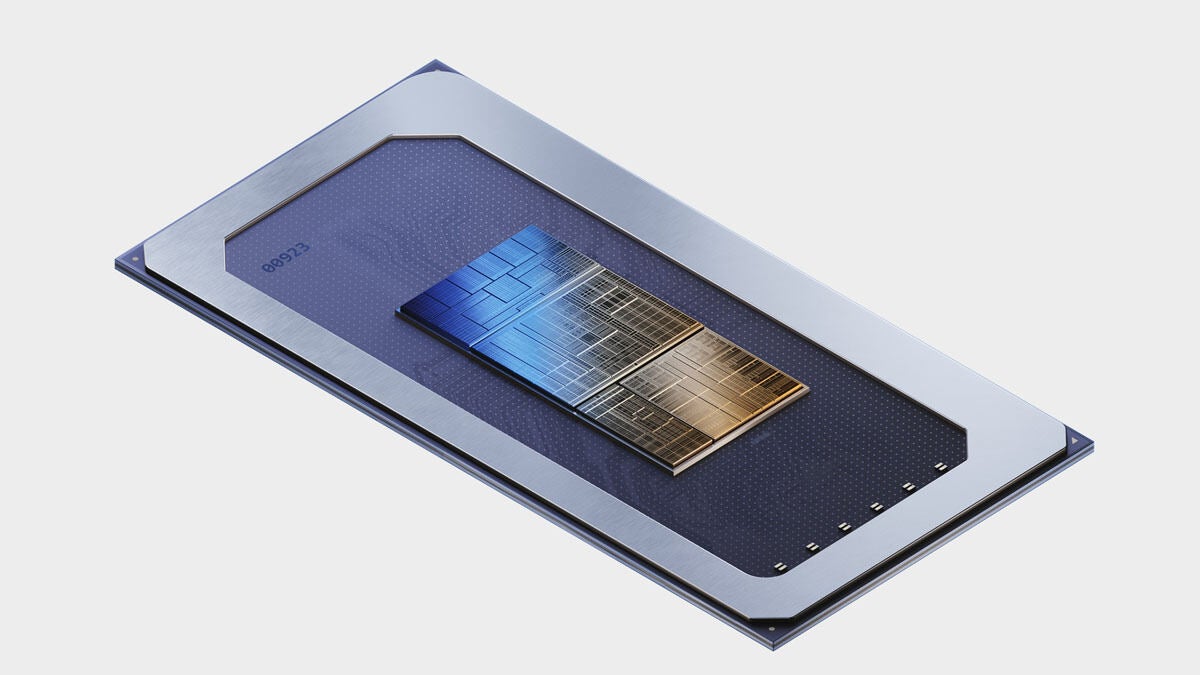

Intel Core Ultra Processor(Meteor Lake)のイメージ図。22nmプロセスでIntelが製造したベースウェハ上にIntel 4プロセスで製造されたCPUチップレット(Intel用語ではタイル)、TSMCの5nmプロセス(N5)で製造されたGPUチップレット、TSMCの6nm(N6)プロセスで製造されたI/Oチップレットなどを搭載し、FOVEROS技術で3D IC実装している (出所:Intel)

Gelginger氏は、「AIの進化はコンピューティングがすべての人にとってより良い未来の基礎となる新たな世界的展開の時代をもたらす。開発者にとって、これは可能性の限界を押し広げ、課題に対する解決策を生み出し、地球上のすべての人々の生活を改善するための大きな社会的およびビジネスチャンスを生み出す」と述べた。Intel Innovationは開発者を対象としたイベントであり、その基調講演で、IntelがどのようにAIの機能を自社のハードウェアに導入して、オープンなマルチアーキテクチャソフトウェアソリューションを通じてアクセスできるようになるのかを示した形で、AIについては「シリコンとソフトウェアの魔法によって可能になる成長経済」である「Siliconomy」を推進していくうえで、どれほど貢献しているのかを強調していた。

Intel18Aは2024年後半に製造準備が整う予定

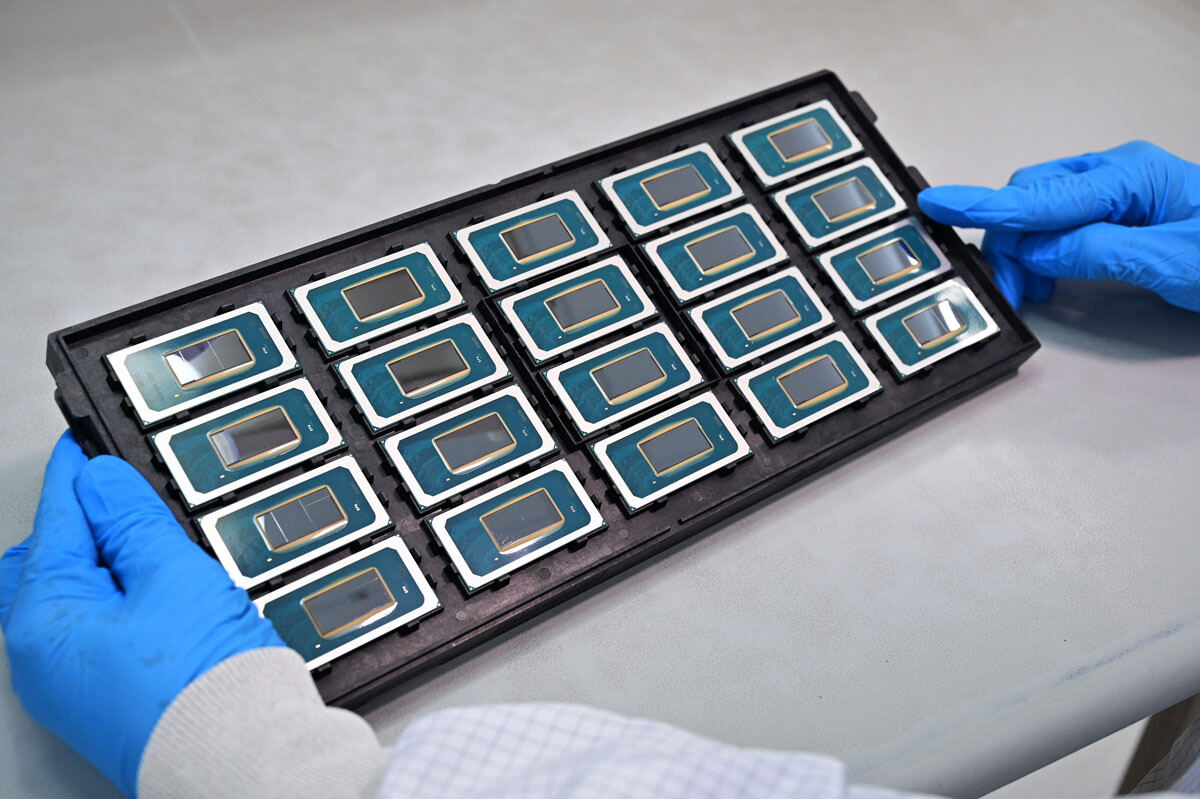

また同氏は自社の4年間で5つの技術ノードを提供するプログラムは順調に進んでおり、Intel 7は大量生産済み、Intel 4も製造準備が整備済み、Intel 3も2023年末の提供に向けて順調に進展しているとし、2024年にはクライアントコンピューティング市場向けに投入する予定の「Arrow Lakeプロセッサ」の最初のテストチップを搭載したウェハも披露した。さらに2024年に導入される予定のIntel 20Aは、基板裏面から電源を供給する「PowerVia」ととGate-All-Around(GAA) FETを搭載した最初のプロセスノードとなる予定で、その改良版となるIntel 18Aについても2024年後半には製造準備が整う予定だとしている。

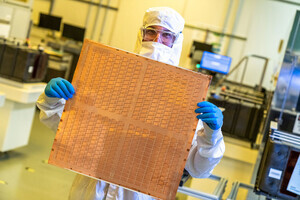

加えて、Intelが今後もムーアの法則を推進するもう1つの方向性として、先般発表したガラス基板などの新しい材料と新しいパッケージング技術の適用も挙げている。2020年代後半にガラス基板が導入されることで、パッケージ上のトランジスタの継続的なスケーリングが可能になり、AIなどのデータ集約型の高性能ワークロードのニーズを満たすことができ、2030年以降もムーアの法則が維持できるとしている。

UCIeでTSMC、Synopsysと協業

なお、IntelはUniversal Chiplet Interconnect Express(UCIe)で構築されたテストチップパッケージも披露している。Gelsinger氏は、「ムーアの法則の次の波はマルチチップレットパッケージで到来するだろうが、オープンスタンダードによってIP統合の摩擦を軽減できれば、より早く到来するだろう」と述べており、2022年に策定されたUCIeスタンダードにより、さまざまなベンダのチップレットが連携して動作できるようになり、多様なAIワークロードを拡張するための新しい設計が可能になると期待されるとしている。

公開されたテストチップパッケージは、Intel 3で製造されたIntel UCIe IPチップレットとTSMC N3Eプロセスで製造されたSynopsys UCIe IPチップレットを組み合わせたもので、これらのチップレットはEMIBを活用して接続されているという。このデモンストレーションについてIntelでは、UCIeを使用してオープンスタンダードベースのチップレットエコシステムをサポートするというTSMC、Synopsys、Intel Foundry Services(IFS)の協業であることを強調している。