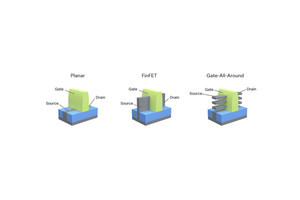

電子デバイスの高機能化にともない、より高性能、より大容量な半導体を低コストで実現する技術の需要は高まる一方です。このトレンドは半導体技術の大きな進歩を促進し、NAND技術はこの10年で2Dから3Dへ移行しました。3次元化への流れはロジックでも始まっておりFinFET技術から、より優れた特性を持つゲート・オールアラウンド(GAA)構造のトランジスタや相補型電界効果トランジスタ(CFET)アーキテクチャへの移行が進みつつあります。将来的にはDRAMもこれに続くと予想されています。ただし「3次元実装」における半導体のスケーリングは簡単なことではありません。電力消費量を抑えながらトランジスタ密度を高めるという課題に取り組む半導体メーカーは、ノードの微細化が進むたびに増大する複雑さに直面しています。

次世代GAA構造トランジスタやDRAMアーキテクチャ、そして今日では200層を超える3D NANDといったデバイスの実現、そしてさらなるスケーリングを行うには製造方法や技術の継続的な進歩が欠かせません。ナノスケールレベルの精度と適切なコスト構造を両立し、持続的にICを製造するソリューションを提供するために、ラムリサーチのようなウェハ製造装置(WFE)メーカーは、プラズマ物理学、材料工学、データサイエンスの限界を押し広げる必要があります。データの力を利用することは、こうした技術を生産に適応する上でゲームチェンジャーになりうることが証明されています。ラムリサーチは装置からよりリッチなデータを収集し、より高度なデータサイエンスの手法を用いることで、膨大な枚数のウェハを再現性良く処理するプロセスへ変換します。

半導体業界が3次元実装の課題に取り組む中、注目すべき5つのトレンドをご紹介します。

多機能のプロセスチャンバーが大量生産に向けてエッチングと成膜の統合を実現

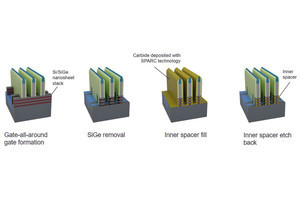

使用される材料がより複雑かつ繊細になり、また成膜および除去に対する要求が垂直と水平の両方向で増加するため、半導体の製造工程はこうした様々な要件を経済的に実行可能な方法で達成できるように進化しなくてはいけません。

複数の機能を単一のプロセスチャンバーで実行することは有望な手段の1つです。成膜やエッチングといった異なる技術を組み合わせて3次元構造の要求に対処する、あるいは3次元形状へのより良いカバレッジやin-situリペアを目的として成膜とエッチングの両機能を統合することなどが考えられます。このようなアプローチにより大量生産という最も困難な状況下においても、より信頼性の高い成膜工程を実現することが期待されます。

高度なロジック半導体チップほど高度な金属インターコネクトが必要

タングステンと酸化タングステンはすでに一部のロジックインターコネクトでダマシン技術による銅配線に取って代わり始めています。3次元実装におけるスケーリングが続いているため、抵抗を下げ電力消費と信号損失を最小限に抑えるには、従来用いられていた金属では限界があるためです。モリブデンなどの代替金属も、特にバックエンドのアプリケーションで研究が進められています。

チップレットの集積がムーアの法則を延命する大規模なスケーリングを実現

シリコンスケーリングがますます高価になることと同様、テクノロジーノード間の従来の開発期間を維持することも難しくなっています。半導体メーカーはチップレットをベースにしたソリューションを採用し、シリコンの限界を超えたスケーリングを実現しようとしています。

システムインパッケージの統合を推進し、ムーアの法則を延命する上でパッケージングは大きな役割を果たしています。TSVエッチングおよびめっきのソリューションは、高度なパッケージングソリューションを実現する高アスペクト比のインテグレーションスキームにおいて重要です。基板をベースとする新たなアプローチも次世代のインターコネクトに対する要求に対応するためには欠かせません。SEMSYSCOの買収によりラムリサーチはパッケージング製品群を拡大し、チップレットとチップレット、またはチップレットと基板とのヘテロジニアス・インテグレーションを実現する革新的な洗浄およびめっき技術を提供します。

データインサイトが運用効率の向上を推進

AIを活用した予測モデリング技術はR&Dを加速し、半導体メーカーをより早く製造段階に到達できるようにするとともに、新しいインサイトと優れた効率性を装置やプロセスの開発者にもたらします。

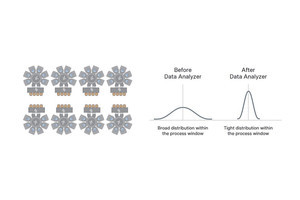

製造工程においてデータはますます重要な資産になってきています。チャンバー内センサーは装置の一貫性を監視し、問題を迅速に検出します。その良い例がラムリサーチの自己認識プラットフォーム「Sense.i」です。

このプラットフォームはデータインテリジェンスと高度なプラズマエッチングをコンパクトで高密度のアーキテクチャで結び付け、生産性の高いプロセス性能を実現します。「Sense.i」プラットフォームは、ラムリサーチのEquipment Intelligenceテクノロジーを活用し、歩留まりを最大化し、ウェハコストを削減するために重要な、とどまることのない進歩を要求される均一性およびエッチングプロファイル制御技術を提供します。

「Sense.i」によって、半導体メーカーはパターン認識を含むデータの取得と分析を行い、改善のために取るべき行動を明確化できます。また「Sense.i」は自動的に較正とメンテナンスを行う能力を特徴としておりダウンタイムと人件費を削減するほか、プロセス変動を最小化しウェハ生産性を最大化するための自己補正を行う機械学習アルゴリズムを提供します。

持続可能なイノベーションがより少ない材料を使用する高性能半導体チップを実現

2030年までに再生可能エネルギー100%を目指し、2050年までにネットゼロを達成するというラムリサーチの2021年目標や、2021年のSEMI半導体気候関連コンソーシアムの設立からもわかるように、サステナビリティの推進はますます重視されています。多くの半導体メーカーは適切な性能とコスト構造を実現するだけでなく、電力消費量を削減し、より少ない材料を使用するという長期的な目標を支える製造装置と技術を求めています。

まとめ

ますます高度な半導体技術を要求する高性能電子デバイスの普及によりWFEプロバイダーと半導体メーカー各社はデバイスや実装の3次元化が進む中、既存の方法や材料を超えた発想を要求されています。新しいアプローチを採用し、豊富なデータを活用する継続的なコラボレーションやイノベーション、そして新たなブレイクスルーがより高度な、そして持続可能な製造技術を推進し、最先端の技術を提供する鍵となります。