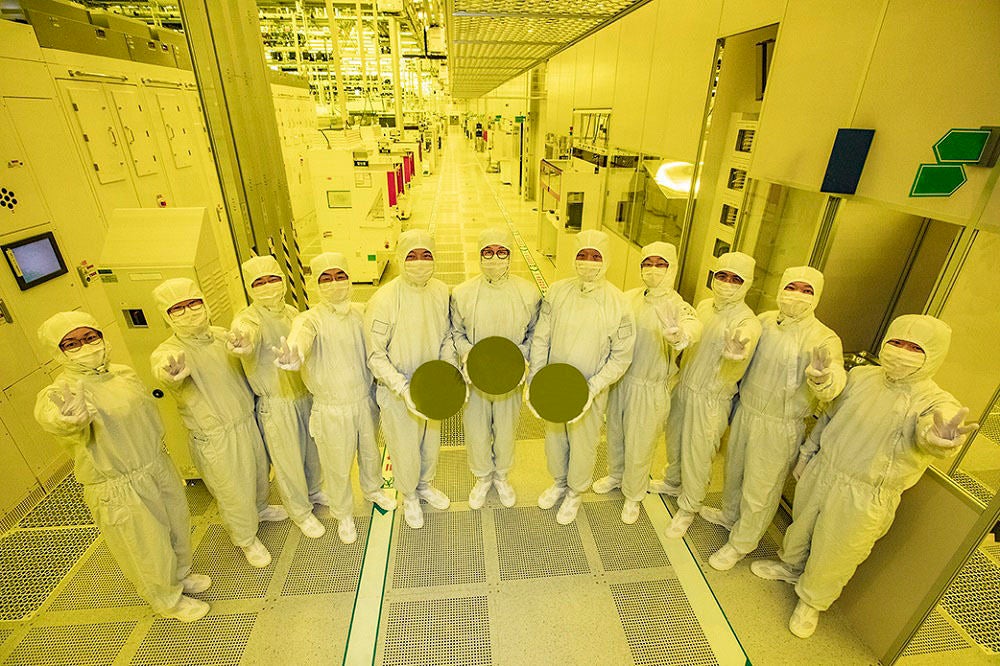

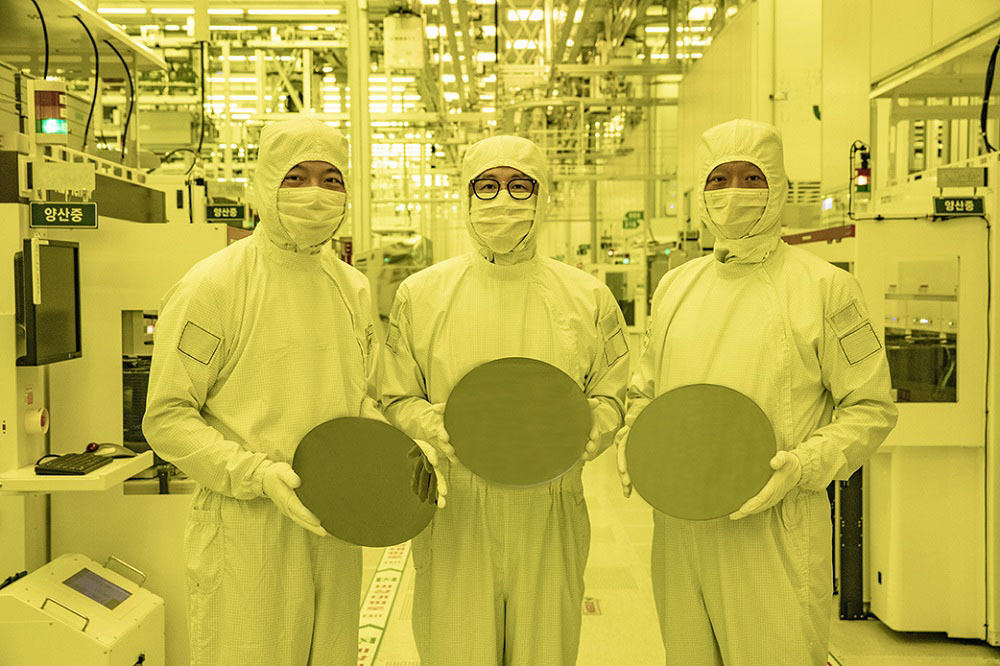

Samsung Electronicsは6月30日、Gate-All-Around(GAA)トランジスタアーキテクチャを採用した3nmプロセスによる初期生産(initial production)を開始したと発表した。

3nmプロセスは、2022年6月30日時点における半導体微細化プロセスにおいて最先端プロセスに位置づけられ、競合であるTSMCは、従来同様のFinFET構造を用いて2022年後半より量産を開始する計画としている。

Samsungは、他社に先行してGAA構造を3nmプロセスで採用することで、技術的優位性を示し、TSMCを追い越す作戦を掲げているが、半導体業界関係者からは、GAA構造は複雑であることから、製造歩留まりが最大の懸念事項になるとみている。

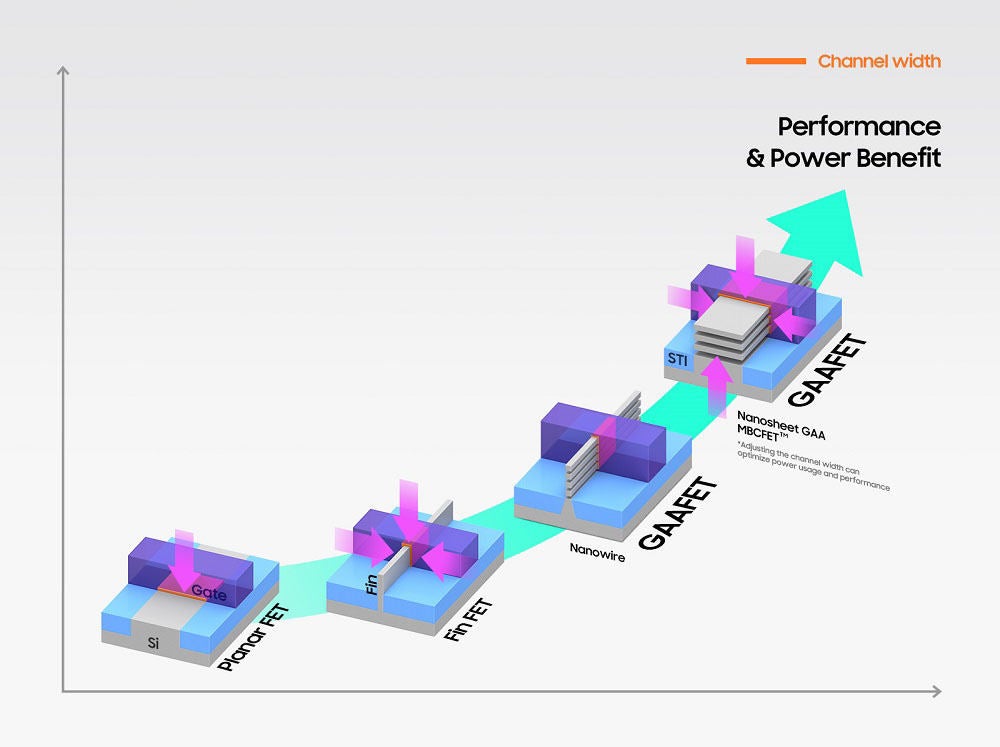

SamsungではMBCFETと呼称する、電流が流れるチャンネルを4方向からゲートで囲むナノシート搭載GAA構造は、従来の5nm FinFET工程に比べて、電力は45%節減され、性能は23%向上、面積は16%縮小しているという。また、次世代となる第2世代MBCFETでは、電力は50%節減、性能は30%向上、面積は35%縮小できるとしている。

さらに、さまざまな顧客のニーズを満たすために電力使用量とパフォーマンスを最適化するために、ゲートが取り囲むナノシートのチャネル幅を調整できるようしており、こうした設計の柔軟性は、設計技術とプロセス技術の同時最適化(DTCO)にとって有利だと同社では主張している。

なお、この3nmプロセスを最初に低電力ハイパフォーマンスコンピューティング(HPC)向けSoCの生産に適用し、その後モバイルSoCなどに拡大していく方針だという。