AMDは「Milan」CPUと「Instinct MI100」GPUを発表しているが、これらのCPUやGPUはエクサスケールスパコン用としては少し物足りない性能であるので、性能アップした後継のCPUとGPUの登場が待たれていた。

これに対する答えとして、AMDは11月に開催したLisa Su CEOの「Accelerated Data Center Premiere」のKeynoteで、「Milan-X」CPUと「Instinct MI200」GPUを発表した。

-

図1 AMDの「Accelerated Data Center Premiere」のKeynoteで、Milan-Xはデータセンタワークロードの処理に挑戦するプロセサであることを強調するLisa Su CEO (出典:このレポートの写真は、すべてAMDのAccelerated Data Center Premiere Keynoteでの発表のビデオをコピーしたもの)

3次キャッシュ容量をMilanの最大3倍に拡張して性能を向上した「Milan-X」

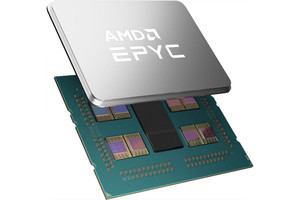

そのデータセンタCPUとして発表されたのが、Milan CPUの3次キャッシュ容量を最大3倍に拡張して性能を向上させたMilan-X CPUである。次の写真は少し見づらいが、半分ずれたパッケージの上蓋の下に見えるのがチップレットで、中央の黒っぽいのはI/OやDRAMインタフェースなどを司るチップレットで左右それぞれに2個ずつ見えるのがCPUコアチップレットである。そして、CPUの上に金属色の放熱板のチップが付いているが、これがMilan-Xで追加された64MBの3次キャッシュの拡張チップである。

なお、この写真ではL3キャッシュの拡張部分だけCPUチップレットの厚みが増えているように見えるが、実際にはダミーのチップレットを付けて厚みを揃え、熱伝導的、機械的にパッケージの上蓋に密着するようになっている。

拡張するL3キャッシュはCPUの真上に置く方が配線は短くできるが、放熱ができなくなってしまうので、追加のキャッシュはCPUの真上を避けて配置したと思われる。

拡張L3キャッシュとCPUチップレットの接続は、AMDの説明ではCuの柱(Piller)同士を押し付けて接続するファンデルワールス力による接続を行っている。AMDの説明によると、このCu-Cu接続はマイクロバンプを使う他社の方法より小さい面積で接続ができるとのことである。

元々のMilanの計算コアに集積された3次キャッシュは32MBであるが、Milan-Xでは32MBのキャッシュブロックを2個追加して合計96MBのキャッシュに拡張されている。

なお、Milan-Xのキャッシュ量は最大804MBと発表されているが、3次キャッシュは全体で768MBで、残りは2次キャッシュなどである。Milan-XのCPUは基本的にはMilanと同じものであるが、Milan-Xでは3次キャッシュとしてV-Cacheと呼んでいる3次元積層のキャッシュメモリが追加されているのが大きな改良点である。

大容量の3次キャッシュが効く例として、AMDは、LSIの物理設計のVerificationの場合で説明している。3次キャッシュが32MBの場合はスループットが24.4ジョブ/時間であったのに対して、96MBの場合は40.6ジョブ/時間で終わり、1.6倍の性能になっているという。

SynopsysのVCSというCAEはLSIに含まれるパターンのサイズや位置関係が正しいかどうかを検証するツールであるが、億の単位のパターンを持つ大規模LSIの設計検証を行おうとすると、キャッシュにはデータが入りきらず、キャッシュに入る量に分割して処理を行うことになる。このため、大きなキャッシュを持ち、キャッシュとDRAMとのデータの入れ替え回数を減らすほど、性能を上げられる。

VCSのライセンスは非常に高額なので購入できるライセンス数は制限される。普通は、徹夜で物理設計のエンジニアがライセンスを順に使い廻すというようなことになる。しかし、サーバの速度が速ければ仕事は早く終わるし、処理速度が速ければVCSの購入ライセンス数も少なくて済むので安上がりでもある。

Milan-Xでは3次キャッシュのサイズが大きくなっているので、若干、アクセス時間が長くなっているが、3次キャッシュの容量が3倍となってヒット率が向上した方の効果が大きく、全体としてはキャッシュアクセスのヒット率が向上し、性能が向上している。なお、VCSのような大量のキャッシュを必要とする処理でなければ、性能が上がるとは限らず、自分の使う処理での性能改善効果は確認しておくのが安全である。

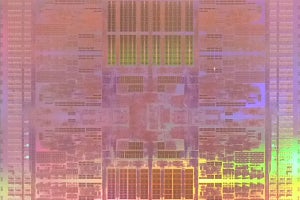

3次キャッシュを3D実装するのはAMDとしては初めてであるが、CPUメーカーが3次元実装などの実装技術を用いることは珍しくなく、AMDもコンスタントに新しい実装技術を取り入れてきている。

-

図3 AMDの3次元実装技術の流れ。2015年にはHBMを混載した実装、2017年にはマルチチップのモジュールを投入、2019年にはCPUコアとI/Oなどのチップレットを分離した実装を行った。そして、現在、3Dのチップレット実装を行った

AMDが採用したCu-Cuダイレクト接続は、通常のパッケージ上の2D接続と比べて200倍以上の密度の接続ができ、3Dのマイクロバンプ接続と比較しても15倍以上の密度の接続ができ、インタコネクトに必要なエネルギー効率は3倍以上であるという。

結果として、Milan-XはL3キャッシュの容量が3倍で、ソケット当たり804MBのキャッシュを持っている。そして、最大64個のZen3コアを集積している。加えてSP3ソケットと互換性があり、前世代のチップをそのまま使う事もできるようになっている。

GPUを2個搭載して性能を向上させた「MI200」

GPUに関しては、図4に示すように、AMDはMI200では、使用するGPUを1個から2個に倍増して性能を引き上げている。グラフィックスではSLIなどでGPUを2個使って性能を上げることが昔から行われており、それの延長で、MI200 GPUではGPUチップを2個使う構成を使っている。しかし、GPUチップを2個使うと消費電力が多くなり過ぎるので、6nmプロセスの採用や、回路的な工夫などで消費電力を抑える努力を行っていると見られる。

MI200 GPU全体では、580億トランジスタを集積しているという。

MI200 GPUにはOpen Compute ProjectのOCP Accelerator ModuleのOAMフォームファクタのものと、通常のGPUのようなPCIeカードのフォームファクタのものが作られる。現状、スパコンで使用するOAMのモジュールはすでにできているが、通常のサーバに実装できるPCIeフォームファクタのMI210は、もうすぐできるという状態であるという。

MI200シリーズのGPUはCDNA 2アーキテクチャになっている。CDNA 2アーキテクチャのMI200シリーズGPUは、Workload-Optimizedコンピュートアーキテクチャとなっているという。最大の計算性能向上はGPUモジュールを2個搭載した点にあるが、それ以外にも科学技術計算用のFP64演算の強化、AI演算用のbf16やINT4/8などの性能向上などが行われている。

また、図6に見られるように、第3世代のInfinityアーキテクチャで4個のMI200 GPUをコヒーレントに接続する機能などが強化されている。

-

図6 AMD Instinct MI200シリーズGPUではCDNA 2アーキテクチャとなり、科学技術計算、AI計算などが強化されている。また、Infinityアーキテクチャで4個のMI200をコヒーレントに接続する機能がサポートされた

次の表1にCDNA 2アーキテクチャのMI250X、MI250GPUと第1世代のCDNAアーキテクチャのMI100GPUとの諸元の比較を示す。

これ以外に、AMDはInstinct MI210というPCIeカード・フォームファクターのボードを出す予定とのことである。また、MI250は208のコンピュートユニットであるが、MI250Xは220コンピュートユニットとなっているのは、MI250Xでは全部のコンピュートユニットが良品のチップレットを使うが、MI250では12個までの不良のコンピュートユニットを許容して歩留まりを上げてコストダウンを行っていると見られる。

前世代のMI100は、コンピュートユニットが120個で、これがCDNA 2アーキテクチャMI250Xでは、220コンピュートユニットと1.83倍になっている。これは、GPUチップが倍増しているので、当然とも言える。しかし、MI100では1.23GB/sであったメモリバンド幅が3.2GB/sと2.6倍に増加している。メモリバンド幅リミットになる計算では、このメモリバンド幅の増加は大きい。

次の図は、第3世代のEPYC 75F3とIntel Xeonの性能を比較したスライドで、Ansysの有限要素法でのメカニカルな解析ではEPYC 75F3が最大33%速い。また、AltairのRadiossで構造解析を行った場合でEPYCが最大34%速く、Ansysの流体解析でもEPYCが最大40%速いという結果になっている。

上でも説明したSynopsysのVCSでの機能検証のMilanと3次キャッシュに3D V-Cacheを追加したMilan-Xの性能比較であるが、右側のMilan-Xでは40.6ジョブの処理を終ったのに対して、32MBのキャッシュだけの場合は、同じ処理時間で24.4ジョブの処理にとどまっている。VCSのような大量のメモリを使うアプリケーションではL3キャッシュ量が大きく効くことを示している。

また、図9はLAMMPSでの原子レベルの動力学シミュレーションでは、NVIDIAのA100 GPUでは8.9M原子ステップ/秒の性能であったが、MI200では19.5M原子ステップ/秒の速度で計算を行うことができたという。これはNVIDIAのA100 GPUに比べて2.2倍の性能であり、MI200は最高性能のGPUであるとAMDは主張している。