「入力バイアス電流」は通常見落としがちなアンプのパラメータの1つですが、アンプ回路の出力精度に大きな影響を与える可能性があります。

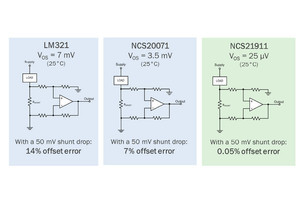

一般に、高精度アプリケーションに関して思い浮かぶ主要パラメータは、入力オフセット電圧、オフセットドリフト、CMRRです。アンプ入力が通常高インピーダンスと考えられる場合、入力バイアス電流はこれにどのように影響を与えるのでしょうか。単純な答えは、入力バイアス電流は経路内のあらゆる抵抗両端に本質的に寄生電圧を発生させ、この影響がアンプで増幅されるというものです。この影響は無視できるほど小さい場合もあれば、回路が全く機能しなくなる場合もあります。特に、電流検出やセンサインタフェースなどの高精度アプリケーションを設計するエンジニアは、確実に堅牢な設計ができるよう、入力バイアス電流の影響を認識しておくべきです。

入力バイアス電流の定義

まず、入力バイアス電流について考察してみましょう。理想オペアンプでは入力端子に電流は流れませんが、実際のオペアンプでは流れます。この値は、データシートの入力バイアス電流(IIB)という仕様で数値化されています。入力バイアス電流により入力にオフセット電圧降下が生じ、出力のオフセット誤差の原因となる可能性があります。ほとんどのアプリケーションでは、この誤差は無視できますが、考慮する必要がある場合もあります。

歴史的に、オペアンプはBJT(バイポーラ接合トランジスタ)で作られてきました。LM324などのバイポーラオペアンプでは、入力の差動トランジスタがオンのときに、ベースとエミッタの間に少量の電流が流れます。言い換えると、ベース-エミッタ電流は、トランジスタのバイアスに必要な電流量ということになります。この電流は、通常ナノアンペアまたはマイクロアンペアの範囲です。PNP入力ペアでは、この電流は入力トランジスタから流れ出します。図1に、バイポーラオペアンプの簡略化したPNP入力段を示します。レールトゥレール入力のバイポーラオペアンプの場合には、NPN入力ペアが追加されています。電流はNPN入力段に流れ込みます。

しかし、最近の大抵の新しいアンプには、CMOSトランジスタが使用されています。MOSFETでは、ゲートは伝導チャネルから物理的に絶縁されているため、真の高インピーダンス入力になります。このようなタイプのアンプには、本当の意味での入力バイアス電流は流れません。それでも、入力バイアス電流のパラメータは、これらのアンプのデータシートで引き続き使用されています。では、この場合、入力バイアス電流のパラメータは何を意味するのでしょうか? CMOSアンプのいわゆる入力バイアス電流とは、ほとんどの場合、ESD構造、保護ダイオード、あるいは寄生接合からのリーク電流です。そのため、オン・セミコンダクターの「NCS20071」などのCMOSアンプの入力バイアス電流は、バイポーラアンプよりもはるかに低い値です。CMOSオペアンプでは、入力バイアス電流は、条件によって正方向にも負方向にも流れる可能性があります。図2に、PMOS入力のCMOSオペアンプの簡略化した入力段を示します。

入力ピンは、それぞれ独自の入力バイアス電流を持っているため、IN+とIN-ピンの入力バイアス電流値は異なる可能性があります。データシートでは、IN+を指す場合はIIB+、IN-を指す場合にはIIB-と記載して、入力ピンの1つを流れる電流IIBを規定している場合があります。2つの入力バイアス電流の数学的な差を入力オフセット電流IOSと呼びます。

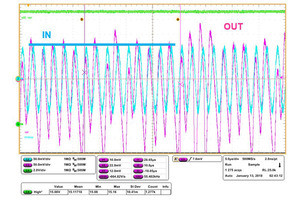

データシートには、必ずしも入力バイアス電流が流れる方向が規定されているわけではないため、電流はピンに流入する場合もピンから流出する場合もありますが、データシートの限界値には絶対値だけが記載されている場合があります。特に記載のない限り、IIBとIOSは絶対値と考えてください。図3に「NCS20071」での、入力コモンモード電圧の変化に対する入力バイアス電流の変化を示します。

入力バイアス電流の影響

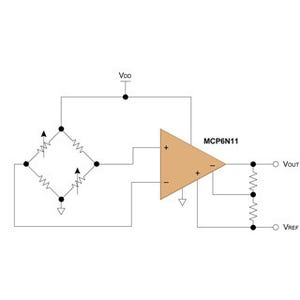

オペアンプ入力に直列に大きな抵抗がある場合、それにIIBが流れオフセットが付加されます。例えば、図4に示す回路図について考えてみましょう。IIB = 10nAの電圧フォロワ回路(ユニティゲインバッファ回路とも呼ぶ)に1MΩの入力抵抗を挿入すると、抵抗の両端に10mVの電圧降下が発生し、10mVの出力誤差が生じます。

IIBによって生じるオフセット電圧を除去するために、回路設計者は、図5に示すようにオペアンプの非反転および反転入力端子両方の入力抵抗を一致させようとすることがあるでしょう。しかし、バイアス電流が一致していない場合、結果として生じる入力オフセット電流(IOS)により入力オフセット電圧が付加されることになります。IOSによって発生するこのオフセット電圧は、出力で誤差の原因となります。非常に小さな入力信号を測定する高精度アプリケーションでは、これが懸念事項となる可能性があります。