5G通信で高性能が求められるパワーアンプ

「太いマジックペンを使って、対数グラフをプロットすれば、ありとあらゆるものがリニアになる」。このいわゆる「マーの法則」(Mar's Law) は、データ測定値を操作することで、いかに実際よりもリニアな特性に仕立てることができるかを皮肉まじりに表現したものです。

しかし、パワーアンプ(PA)で高いリニアリティを達成するには、そのような手っ取り早い方法はありません。PAは、携帯電話の通信インフラにおいて非常に重要な役割を果たしています。特に5Gのセルラーモバイル通信(図1)の導入が進むにつれて、PAの性能要求はさらに厳しくなります。

本レポートでは、5G通信技術によって実現するとされる機能や利点、およびそれにともなってPAの設計に課される要件について説明したいと思います。

さらに、最も一般的なPAリニアライゼーション手法について検討し、それらがPAの要件を満たす上で適切であるかどうかを評価します。その後、低消費電力のリニアライザICを取り上げ、それが5GアプリケーションにおけるPAの消費電力を削減しつつPAの設計を簡素化する可能性について考えてみたいと思います。

5Gの設計課題

5Gは、いくつもの点で現行の通信技術より優れているとされます。より多くのユーザーがより高いデータレートを同時に利用可能になる上、モバイル機器のバッテリ寿命も延長されます。これを実現するには、PAは可能な最高の効率で、かつ従来よりも広い帯域幅(最大100MHz)で動作する必要があります。

アンプのリニアリティ

PAが完全にリニアであれば、必要な入力信号のみを増幅して出力できるはずです。しかし、現実には、そのようなPAは存在しません。実際にはノンリニアであるため、出力信号が歪められ、アンプが飽和点に近づくにつれて歪みは増大します(図2)。

マルチトーン入力信号を印加した場合、ノンリニアであるために、不要な相互変調周波数がPAの出力に現れます(図3)。

PAの歪みを低減するには、何らかのリニアライゼーション手法を利用する必要があります。以下のセクションでは、5G環境における最も一般的なリニアライゼーション手法の動作と適合性について説明します。

バックオフ

最大出力電力レベルを制限して、信号全体をPAの伝達曲線のリニア領域に収める手法は、一般に「バックオフ」と呼ばれています。この比較的単純な手法の難点は、PAの動作ポイントが飽和点から離れるにつれて、PAの効率(DC電源をRFエネルギーに変換する能力)が低下することです。

一部のシステムでは、信号のピーク平均電力比(PAR)の要件を満たすために必要なバックオフによって、PAの効率が8%にまで低下する場合もあります。その結果、消費電力とシステムの実装コストが増大し、大型のヒートシンクも必要になります。そのため、バックオフは5Gアプリケーションで許容可能な効率を達成するための適切なリニアライゼーション手法ではありません。

アクティブ・リニアライゼーション

効率を低下させることなくPAのリニアリティを向上させるには、「プリディストーション」と呼ばれる一種のアクティブ・リニアライゼーションが必要です。この手法では、PAの固有のノンリニアリティによって引き起こされる歪みの量を「予測」し、その反転信号を信号経路に注入することにより、アンプ出力において必要な信号に対する不要な信号の比率を低減します(図4)。これは隣接チャネル漏洩電力比(ACLR)として規定され、少なくとも-50dBcである必要があります。

一般的なアクティブ・リニアライゼーションのタイプとしては、デジタルプリディストーション(DPD)とRFパワーアンプリニアライゼーション(RFPAL)の2つが挙げられます。

DPD

図5に示すとおり、デジタルプリディストーション (DPD) では、シグナルチェーンの最も初期のポイント(デジタルベースバンド)において、必要な信号にプリディストーション補正信号を追加します。

DPDシステムはいくつかの方法で実装することができます。全機能内蔵のバージョン(ベースバンド、デジタル、RF搭載)が利用可能である一方、別個のデジタルベースバンドとディスクリートRFを使用するソリューションもあります。

さらに別のソリューションでは、FPGAとRFトランシーバ(およびDPD測定経路)で構成されます。しかし、RFトランシーバは入力信号帯域幅の5倍の周波数で動作する必要があり、設計の複雑さ、実装面積、および消費電力(5W typ)が増大するため、小型の低消費電力アプリケーションで使用する場合、DPDは適切なリニアライゼーション手法とはいえません。

RFPAL

図6は、RFパワーアンプリニアライゼーション(RFPAL)と呼ばれる、もう1つのアクティブ・リニアライゼーションおよびプリディストーション手法を利用したシステムの高レベルのブロック図を示しています。

この手法では、スタンドアロンのRFIN/RFOUTアーキテクチャとアダプティブRFプリディストーション技術を利用し、補正信号を必要なポイント、つまりPAの入力にのみ注入することができます。

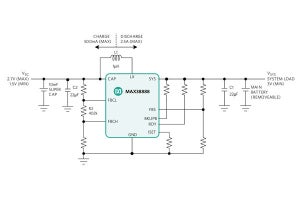

それは、このシステムがDPDシステムと比べてはるかにシンプルかつ小型のトランスミッタとベースバンドで構成され、より低い周波数(入力信号帯域幅)で動作可能であり、消費電力も少ないということです。最近まで、RFPALを使用した最大のリニアライズ入力チャネル帯域幅は、わずか60MHzでした。図7は、この問題を克服する新しいRFPAL ICを示しています。

このデバイスは動作周波数範囲が最大3.8GHzであり、リニアライズ入力信号帯域幅は最大100MHzです。消費電力は1280mWで、DPDソリューションと比べて最大70%低減されます。図8は、このリニアライザを使用した標準的なPAについて、測定したACLRと効率の性能(5つの不連続な20MHz LTEチャネル、PAR 10dB)を示しています。

出力電力レベルが37dBmの場合、このPAの効率は23%、ACLRは-50dBです(RFPALがオフならACLRは約8dB向上)。さらに、このRFPALデバイスは広く利用されている複数のPA(A級、AB級、ドハティ)で評価されているため、実質的に「プラグアンドプレイ」ソリューションであり、設計の簡素化、開発期間の短縮、リスクの低減につながります。

このICは9mm×9mmのQFNパッケージで提供されているため、ソリューション全体のサイズ(電源、ヒートシンク、筺体を含む)は6.5cm2で済みます。さらに、最大6GHzまでのアプリケーションにおいて、必要な場合、リニアライズされたPAの信号を、ミキサを使用してアップコンバートすることができます。

5G通信機器を構築するために必要なもの

5G通信機器は、かつてないほど広い帯域幅と高効率で動作することが求められます。使用するPAのリニアリティと効率は、これらの要件を満たす上で極めて重要となります。

今回、最も一般的なPAリニアライゼーション手法のいくつかについて検討しました。バックオフが5G設計での利用に適さない一方、DPDをアクティブ・リニアライゼーション手法として利用すると、総合的なリニアリティと効率が向上することを示しました。

しかし、DPDは複雑な手法であるため、システム全体の消費電力の増大とソリューションの大型化につながります。結論として、小型のプラグアンドプレイRFPAL ICを使用すれば、よりシンプルかつ低消費電力のリニアライゼーション手法を実現することができます。このICは、最大100MHzまでの入力信号帯域幅に対してPAの効率を向上させます。このデバイスは、幅広いアプリケーションにわたって、さまざまなアーキテクチャ(A級/AB級/ドハティ)、プロセス(GaAs、GaN、InGa)および周波数(698MHz~3.8GHz)のPAでの使用に適しています。このデバイスは、5Gのインフラをはじめとするアプリケーションに最適な選択肢となります。

著者プロフィール

Thomas MaudouxMaxim Integrated

コア製品事業部のセンサー担当の技術者。

半導体業界で20年以上の経験があり、ジョージア工科大学で電気電子工学の修士号を取得。

Michael Jackson

Maxim Integrated

アナログIC設計技術者として20年以上の業務経験があり、Maxim Integratedでシニアテクニカルライターを務める。

ダブリンシティ大学で電気電子工学の修士号を取得。