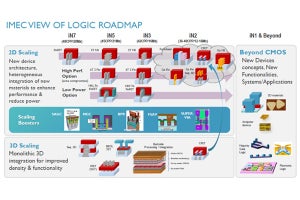

ベルギーの独立系半導体ナノテク研究機関Imecは7月8日(米国時間)、米サンフランシスコで開催された同社の年次研究成果発表イベント「ITF USA 2019」において、3nmロジックテクノロジノードに対応するデュアルダマシン21nm M2(第2層メタル)ピッチテストチップの測定結果を発表した。

-

ITF USA 2019で公開された21nm M2メタルピッチテストチップに関するデータ。テストチップの構造(左上)、メタルピッチ数値、マスク、使用リソグラフィの説明(左下)、信頼性に関する実験データ(中央)、RC遅延の実験データ(右上)および測定で得られた諸特性(右下) (出所:Imec)

このテストチップは、信頼性に影響を与えることなく、前世代のCu配線と比較してRC(抵抗・容量積)が30%向上し、さらに330℃の高温でも530時間後においてもエレクトロマイグレーションによる不良は観察されず、MOSデバイスのゲート絶縁破壊(TDDB)測定でも、100℃で不良が発生するまでの時間は10年以上と見積もられたという。

今回の成果についてImecは、自己整合ビアや自己整合ブロックなどのスケーリングブースターを3nm以降の配線技術で実装する必要性が実証されたとしている。

今後、従来のフロントエンド(FEOL、トランジスタ形成工程)技術の寸法スケーリング(比例縮小化)は減速すると予想されているが、一方のバックエンド(BEOL、多層配線形成工程)の寸法は要求される面積スケーリングに追いつくために技術ノードの進化とともに約0.7倍で縮小し続けている。3nmロジックテクノロジノードでは、BEOL性能を維持したまま21nmという狭い金属ピッチのM2相互接続層を製造する必要があるとされており、これは、高い信頼性を維持しながら、RC遅延を厳密に制御することが求められることを意味するが、今回の成果により3nmノード以降のBEOL多層配線構造の微細化に向けた道が開けたとImecでは説明している。

ArF液浸の4重パターニングとEUVLのハイブリッド

M2層をパターニングするために、波長193nmのArF液浸ベースの自己整合四重パターニング(SAQP)とEUVリソグラフィ(EUVL)が併用されたという。具体的には、ArFでラインとトレンチをパターニングし、EUVLでブロックとビアをパターニングしたという。テストチップには、バリアのないルテニウム(Ru)配線および比誘電率k=3.0の層間絶縁膜が採用された。

また、今回の成果を受けて、埋め込み電源レール、SuperVia(配線層を飛び越えて接続するための高アスペクト比の長いビア)、自己整合ブロック、完全セルフアラインビア、ダブルセルフアラインブロックなどのスケーリングブースターを追加することで、BEOL多層配線の性能を今後も改善できることが示されたとImecのナノインターコネクト担当プログラムディレクタであるZsolt Tokei氏は述べている。

さらに同氏は、「3nmおよびその先の相互配線:さらにBEOL微細化を進めるための道具箱」と題する講演にて、3nm技術ノード(Imec用語でiN3)以降のBEOL多層配線実現のために、今後、SuperVia、バリアレスエアギャップ(AG)を用いたセミダマシン、配線層内への薄膜トランジスタ埋め込みはじめさまざまな新たな技術導入を検討していくとしている。今回の研究では、もはや微細化の限界といわれていたデュアルダマシン構造を採用したが、実際の3nmロジックデバイスで使うとは限らないようである。

-

Imecが3nm技術ノード(iN3)以降のBEOLで採用を検討している技術のロードマップ。左から、従来通りのデュアルダマシン構造(ArF液浸による多重露光とEUV露光の使い分け)、スーパービア(配線層を飛び越えたビア)、RC向上のためバリアレスAG(エアギャップ)を採用したセミダマシン、配線に新たな機能付加のための多層配線中への薄膜トランジスタ埋め込み (出所:Imec)

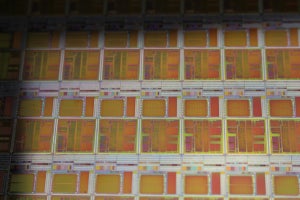

なお、ImecはITF USA 2019において、21nmだけではなく16nmメタルピッチ構造の断面SEM写真も公開したが、これはまだメカニカルサンプルの段階で、材料・構造最適化や電気特性最適化はこれからのようである(図4参照)。こうした成果を踏まえ、FEOLの微細化は減速してもBEOLの微細化は今後も従来のペースで進むとImecは主張している。