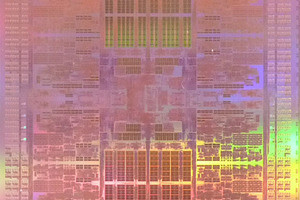

Cadence Design Systemsは4月22日(米国時間)、TSMCと協業し、TSMCの5nm FinFETプロセステクノロジー上で開発されるモバイル、ハイパフォーマンスコンピューティング(HPC)、5G、AIアプリケーション向け次世代SoCの設計に向けた支援を行っていくことを発表した。

同協業の一環として、Cadenceのデジタル設計、サインオフ検証、およびカスタム/アナログ設計ツールが、Design Rule Manual(DRM) およびSPICE v1.0認証を取得し、CadenceのIPがTSMC 5nmプロセスで利用可能になったという。

また、ツール、フロー、メソドロジーを特長とするプロセスデザインキット(PDK)も従来のオンプレミス環境およびクラウドベース環境双方にて利用可能になったともしている。

TSMCの5nmプロセスではEUVが本格的に採用されるが、Cadenceのデジタル設計およびサインオフツールは最適化がなされているため、サポートが可能だとCadenceでは説明。すでに複数の顧客が同社のツール、フロー、IPを活用する形でTSMCの5nmプロセス上にて実製品の設計のテープアウトを完了しているとしている。