ムーアの法則、プロセスの微細化によるトランジスタ素子の集積密度の向上が物理的な限界を迎えつつある現在、その集積化を継続させるためのさまざまな取り組みが各所で進められている。

例えば半導体実装(パッケージング)分野では、2.5Dおよび3D積層技術を用いて3次元的に集積度をあげる方式が多くの半導体企業で採用されている。最初の積層技術として登場したThrough-Silicon Via(TSV:シリコン貫通ビア)は、3Dスタックメモリ、GPU、FPGA、CMOSイメージセンサ(CIS)など、さまざまな半導体デバイスで活用されるようになっている。

積層実装市場は年平均27%で成長

現状、HBMやCISといった半導体製品分野がTSV市場の大部分を占めている。仏Yole Développementは、2月20日発行予定の調査レポート「2.5D / 3D TSV & Wafer-Level Stacking: Technology & Market Updates report, 2019 edition」の中で、「積層実装市場は今後、年平均成長率27%で成長し、2023年には55億ドルを超える」と予測している。現状のTSV向けアプリの最大市場はコンシューマ向けであり、TSV市場全体の65%以上のシェアを占めている。しかし、今後、もっとも勢いを見せ、市場拡大の推進役を果たすのはHPC(高性能コンピューティング)カテゴリともしており、市場シェアも2018年の20%から2023年には40%へと拡大すると予測している。

-

積層実装技術の応用分野別市場規模の2018年から2023年への変化。市場規模の大きい順に、HPCおよびネットワーキング、コンシューマ、産業・医用・その他、自動車 (出所:Yole Développement)

積層実装市場を二分するTSV利用技術とTSV不要技術

今日のハイエンド向け積層実装市場にとって、もっとも人気のある2.5D/3D積層技術は、3Dスタックメモリ用のTSV、ならびに異種チップ積層用のTSVである。TSMCの「Chip-on-Wafer-on-Substrate(CoWos)」技術はすでにHPC分野で広く使用されており、2019年には新しいTSV技術、例えばIntelの「Foveros」が登場する予定である。これはTSVインタポーザおよび3D SoC技術をベースにしており、ハイブリッドボンディングとTSV相互接続を用いている。 Foverosの例は、TSVがTSV以外の技術の挑戦にさらされているにもかかわらず、依然としてTSVが信頼されていることを示しているとYole Développementは判断している。

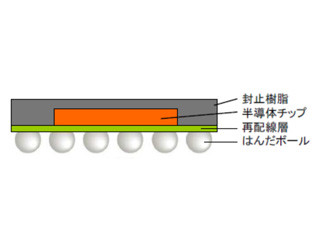

しかし、TSVを必要としない技術が市場に登場することを無視することはできないとも指摘している。この技術革新は「基板上」と「基板内埋め込み」の2つのグループに分けることができる。すでに商品化されている「EMIB(Embedded Multidie Interconnect Bridge)」技術は、Siブリッジが基板内の奥深くに位置している基板内埋め込みグループに属する。他の技術、例えば「Integrated Thin Film High Density Organic Package(I-THOP:集積薄膜高密度有機パッケージ)」および「Flip Chip - Embedded Interposer Carrier(FC-EIC:フリップチップ - 埋め込みインターポーザキャリア)」なども開発されているが、まだ市場に出ていない。

Appleのプロセッサで広く使用されている「InFO on Substrate」など、TSVを用いない技術の活用も進んでいる。また、現在、開発が進められている再配置層(RDL)インターポーザ技術は、2020年までに市場に出る予定であるほか、2016年に「FOCoS(Fan Out Chip on Substrate)」が開発され商品化されたが、こちらの受注量は多くはないのが現状である。

ハイブリッドボンディングは、2つのカテゴリ(TSVあり/なし)を橋渡しできる技術であり、2016年以降、スマートフォンのCISで一般的に使用されている。ハイブリッドボンディングは、近い将来、ハイエンド市場向けのメモリと2.5D積層構造を相互接続するために使われる可能性が高いという。

競い合う積層実装業界の動向

現状、ファウンドリ、IDM、OSAT、IPベンダの4つの異なるビジネスモデルの企業が、積層実装業界で競争している。

TSMC、UMC、およびGLOBALFOUNDRIESのようなファウンドリは、シリコン・インターポーザを社内で生産することができるため、TSVの異種チップ積層分野を支配している。 Intelは、独自の「Foveros」を開発して、この分野で競争しようとしている唯一のIDMである。

3Dスタックメモリ分野では、Samsung、SK Hynix、Micronの3大IDMの間で戦いが繰り広げられている。これらの企業は、今後とも3Dスタックメモリ市場を支配し続けるだろうとYoleは見ている。

一方、3D SoCはファウンドリだけが保持している技術である。高い歩留まりを確保し、リスクを抑えるために、1つのファウンドリ内ですべて一貫処理される。この分野では、TSMCがTime-to-Marketの短さでGLOBALFOUNDRIESに勝っているとYoleは指摘している。

TSVを用いない技術では、ファウンドリ、IDM、OSAT、そしてプリント基板メーカーの間で激しい開発競争が展開している。 Samsung、Intel、TSMCなどの一部の企業は、TSVの「あり」と「なし」の両方の技術開発に関わっている。代表的なOSATであるASEは2016年にFOCoS技術を市場に投入した。一方、Amkorはじめ他の企業も技術開発をおこなってきているが、まだ注文に応じる状態にはないようだ。

新光電気、Unimicron、富士通インターコネクトテクノロジーズなどのプリント基板メーカーはまだ研究開発中の段階にある。 IP企業のXperiは、ハイブリッドボンディング技術が「TSVありにもTSVなしにも対応可能なため有利な立場にある。 Xperiのもう1つの利点は、その技術がハイエンドとミッド/ローエンドの両セグメントに適用できることである」と説明するなど、自社技術の優位性をアピールしている。

なおYoleは、OSATに比べて、ファウンドリ、IDM、およびIP企業が積層実装技術分野では優位な立場にあるとしている。OSATは、伝統的にウェハの後工程を担ってきた存在であるため、ウェハプロセス処理工程と切り離すことが難しい積層実装の分野で受注を獲得するのが困難であるため、という判断である。