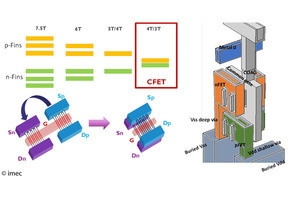

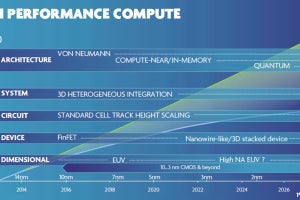

半導体研究機関であるベルギーimecは、5nmノードのSRAMおよびSTT-MRAMをラストレベルキャッシュとして用いた場合の電力・性能・面積の比較をIEDM 2018にて発表した。

今回の発表ではSTT-MRAMが、高性能コンピューティング分野のラストレベルキャッシュの性能要件を満たしていることがわかったばかりではなく、メモリ容量が大きくなるほどSTT-MRAMはSRAMに比べて消費電力を減らせることがわかったという。

CMOSプロセスの微細化に併せて工程が複雑になるにつれ、高密度なSRAMセルの微細化が難しくなってきていることが知られているが、STT-MRAMは、こうしたSRAMベースのラストレベルキャッシュを置き換える、より低消費電力な素子候補の1つとなっている。

今回の発表では、5nmノードのSTT-MRAMがHPC分野に適用できるかの検討として、5nmのSTT-MRAMセルの要件と仕様の定義に向け、設計とプロセスの同時最適化(DTCO)を実施。その結果、複数の必要要件を導き出したとするほか、それらをもとに、実際に300mmウェハ上にSTT-MRAMセルを作製、特性測定の実験を実施し、必要とされるSTT-MRAMセルサイズは、SRAMマクロ(SRAMとして必要な機能をすべて持った最小構成のチップ)サイズの43.3%と半分以下の面積で済むことを確認したという。

なお、imecのSTT-MRAMプログラムディレクターであるGouri Sankar Kar氏は、「今回行なったDTCOとSi検証モデルにより、STT-MRAMの電力効率は、SRAMと比較して、読み込みでは0.4MBから、書き込みでは5MBから上の容量で高くなるとの結論が得られた」と説明しており、HPC分野での要件を満たすことができると考えられるとしている。