imecは、既存の配線材料であるCuやCoが3nmプロセスノードでも使えることを確認したことを明らかにした。

これは、6月4~7日(米国時間)に米国カリフォルニア州サンタクララにて開催されている「2018 IEEE International Interconnect Technology Conference(IITC 2018)」おいて、CuやCoダマシン配線の延命からRuやグラフェンなどの代替材料の評価に至る11件の次世代インターコネクト(相互配線)技術論文を通じて発表されるものとなる。

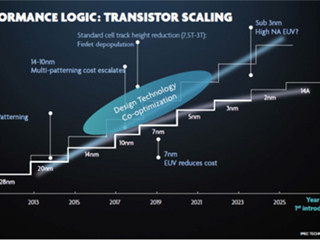

過去約20年の間、Cuベースのデュアルダマシンは、信頼性の高い相互接続を構築するプロセスフローとして広く使われてきた。しかし、ロジックデバイスを5nmおよび3nmプロセスに縮小しようとすると、厳密に設計されたCu配線の抵抗と信頼性要件を満たすことは、従来以上に困難になるとされてきた。一方で、半導体業界としては、現状のダマシンプロセスを可能な限り延命することで、技術コストの上昇を抑えたい思惑があり、さまざまな解決策の模索が進められてきていた。

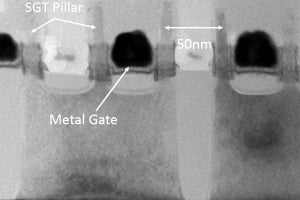

imecでも、プロセスの限界を見極めるために、さまざまな微小寸法のダマシン構造を構築。Cu配線の抵抗をCoならびにRu配線の抵抗と比較し、300nm2(または12nmの線幅)までの配線断面積についてはCuが依然として優れていることを実証したとする。

これは 3nmプロセスに相当する値で、信頼性要件を満たすための選択肢の1つとして、TaNなどの薄い拡散バリアおよびCoまたはRuなどのライナーと組み合わせてCuを使用することが挙げられるとのことで、中でもTaN拡散バリアは、高いCu拡散バリア特性を維持しながら2nmプロセス未満までシュリンク可能であることも示されたという。

また、Cu幅が15~12nmの範囲におけるシステムレベルの性能への相互接続ラインエッジラフネスの影響を調べたところ、ラインエッジラフネスは短いCuワイヤの抵抗分布には影響を与えるがものの、システムレベルではその影響は平均化されることも確認したとする。

なお、従来のダマシンプロセスを拡張する代替策としては、配線断面積およびビアを小さくするにつれて抵抗値がCuよりも低く抑えられる利点があるCoへの置き換えが提案されている。Coには拡散バリアが必要だが、バリア膜そのものは、すでに長年持ちいれている技術であり、その点での問題は少ないと見られる。また、さらに性能を向上しようと思った場合の改善策としては、界面科学を駆使した最適化をはかり、Coをバリアフリーにするか、もしくはバリア膜の膜厚をサブナノオーダーに抑えることが挙げられるとしている。さらに、imecでは、エレクトロマイグレーションと蓄熱実験によるCoの信頼性に影響を及ぼすメカニズムの研究も実施。バリアのないCoビア内にボイドが発生しないことを確認したとのことで、これらの結果として、Coが微細化が進む今後の半導体プロセスにおいて、より優れた能力を示すことが期待できるとしている。