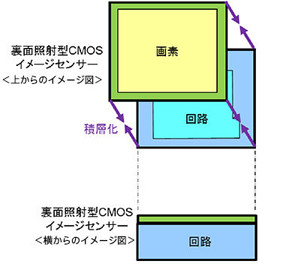

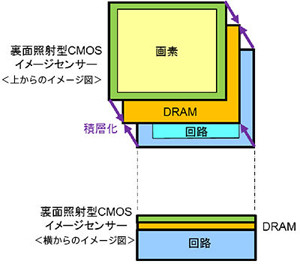

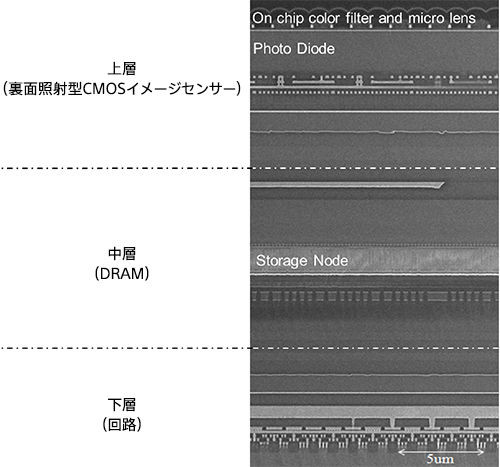

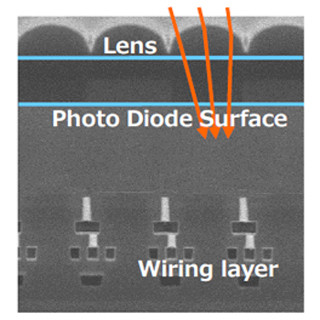

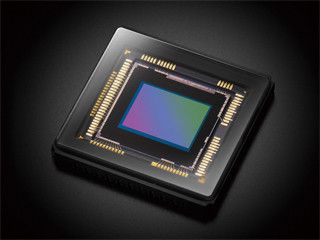

ソニーは2月7日、従来の裏面照射型画素部分と信号処理回路部分との2層構造の積層型CMOSイメージセンサに1GビットのDRAMを積層した3層構造のスマートフォン(スマホ)向けCMOSイメージセンサを開発したと発表した。詳細は2017年2月5日より米国サンフランシスコで開催されている「国際固体素子回路会議(ISSCC 2017)」にて発表された。

同イメージセンサは、従来の回路と画素部の間にDRAMを挟みこむ構成で、1930万画素サイズの静止画1枚を従来比で約4倍となる120分の1秒で読み出すことを可能とした。これにより、画素の行ごとの読み出し時間のずれを抑えることができるようになり、露光時間を制御するメカニカルシャッターのないスマホでも、動きの速い被写体の撮影時に起こりやすいフォーカルプレーン歪みを抑えた静止画の撮影が可能になるとしている。

また、高速読み出しが可能になったため、フルHDサイズで従来比で約8倍となる毎秒最大1000フレームの動画撮影も可能となる。DRAM上に蓄積された撮影データを、外付けのISP(イメージシグナルプロセッサ:画像処理回路)を通すことで、通常速度の動画とスローモーション動画をシームレスにつないだ作品を作ることが可能で、スローモーションによる撮影の瞬間を逃がさないことを目的とした、被写体の急激な変化を検知し、高速撮影を自動的に開始するモードなども設定可能だという。

なお同社では、3層それぞれの回路間のノイズ低減など、設計上の技術的課題も克服しており、高品質と高い信頼性も実現したとしている。

スーパースローモーションのサンプル動画