今年のIDFに合わせ、RAMBUSはDDR4 DIMM向けのChipsetの製造販売を行うことを発表した。これに関する説明会が8月31日に都内で開催されたので、これに合わせて内容をご紹介したい(Photo01~03)。

|

|

|

|

Photo01:日本法人であるラムバスの代表取締役社長を務める鈴木広一氏。今回は冒頭の挨拶のみ行った |

Photo02:Linda Ashmore氏(Director, Corporate Communications)。記事には書いてないが、2013年の発表会の時にも同席されていた |

Photo03:今回の主役であるEly Tsern博士(ViP, Memory Products, Memory+Interface Division)。Chief Technologystの肩書きもお持ち。ちなみにマーケティング的な質問に対しては、同席されたSamira Naraghi氏(Director, Product Marketing)が対応された |

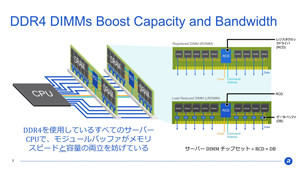

さて、説明の順序がちょっと本来のプレゼンテーションと異なるが、まずはChipsetとは何ぞや? という話から。これまでDIMMの話をするとき、Unbuffered DIMMとRegistered DIMMの2種類があり、これに加えてDDR4世代では新たにLRDIMM(Load Reduced DIMM)というものが加わった。この構造を示したのがPhoto04のスライドである。Unbuffered DIMMは名前の通り一切Bufferがない(信号線とDRAMチップが直結されている)構造、Registered DIMMとLRDIMMはどちらも間にBufferが入る構造である。

そもそもなんでBufferが必要か? というところから。一般論として1つの信号線に複数のデバイスがぶら下る場合、信号が高速化すると波形の乱れが大きくなりすぎる。この結果としてある程度以上に速度を上げられなくなる、という弊害が発生する。DIMMの場合、信号線そのものは1つの信号線が1つのメモリチップに直結しているだけだが、Clock信号あるいはCommand/Addressといった信号は1本の信号線を分割してDIMM上のすべてのDRAMチップに供給する必要があり、高速化に際してはまずここがボトルネックになる。そこで、DIMMの上に専用のBuffer(RCD:Register Clock Driver)を搭載、Clock信号とCommand/Address線の信号を一旦受け、これを整えてDIMM上のDRAMチップに再分配するという方式が実装された。これがいわゆるRegistered DIMMである。

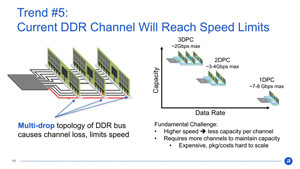

ところがDDR4世代になってさらに信号が高速化すると、データ線の側にも対策が必要になってきた。これは特にサーバ向けに大容量構成となるDIMMで顕著になった。というのは、1枚のDIMMの上に、データ線を共有する形で2つ以上のDRAMチップが接続される場合があるからで、これをカバーするためにデータ線にも専用のバッファ(DB:Data Buffer)を搭載することになった。この結果として、LRDIMMでは相対的に信号波形の乱れに強くなったため、例えばJEDECの推奨であればDDR4-2266まではRegistered DIMMでも1chあたり2枚のDIMMが装着可能なのがDDR4-2400では厳しい(ので1chあたり1枚に制限される)のに対し、LRDIMMでは1chあたり3枚も可能としている。DIMMスロットがあること自身が波形の乱れの大きな要因でもあるため、Unbuffered DIMMあるいはRegistered DIMMではデータ波形が大きく乱れない範囲で利用する必要があり、2400MHzあたりだとこのDIMMスロット自身による乱れが大きくなりすぎてしまう、というのが1枚に制限される理由だが、LRDIMMだと多少の波形の乱れはDBが吸収してくれるので、無理が効くという訳だ。勿論LRDIMMでも幾らでも高速化できるというものでもないのだが、Registered DIMMよりはマシという訳だ。このあたりを簡潔にまとめたのがPhoto05である。

|

|

Photo05:これは今年のIDFにおけるRAMBUSのSponsor Sessionの資料から。数字は割とラフなものだが、LRDIMMでも3DIMM/chなのは2Gbpsのオーダーで、3Gbps以上だと2DIMM/chに、それを超えるとあとは1DIMM/chに制限される。DPCは"DIMMs Per Channel"の略 |

さて、このDDR4向けのChipset(つまりRCDおよびDB)で比較的大きなシェアを持っているのはIDTであり、次にTIとかInphi、Montage Technologyが来る。TIはDDR3の世代までは結構広く使われていたが、DDR4の世代ではややシェアを落としている感じである。Inphiも同様にDDR3世代では随分頑張ってシェアを握っていたのだが、DDR4世代ではやや出遅れている。その代わりにDDR4世代ではMontageが相対的に大きなシェアを握ることに成功したというべきか。今のところ、Chipsetの提供を公式に行っている(というか、DIMMモジュールメーカーが認知している)のはこの4社のみである。これは例えばSK HynixのLabel Informationページを見ると判りやすい。このページの最後にDDR4モジュールのオプションコードの一覧が載っているが、T1/T2がMontageのRCD/DB、T7がTIのRCD/DB、TD/TEがIDTのRCD/DB、TLがInphiのRCD/DBを使っていることを示している。要するにDIMMモジュールメーカーからすると、この4社の製品のみを使うと明らかにしている訳であるが、RAMBUSはここに5社目として参入しようと考えているわけだ。