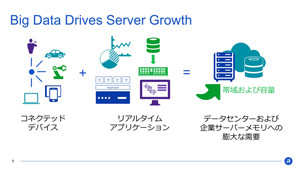

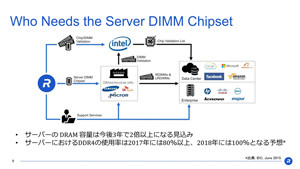

という訳で長い前置きになったが、いよいよ本題。そもそもなぜDDR4のChipsetビジネスに参入したのか、という理由についてRAMBUSは今後もサーバのニーズが非常に堅調であることを挙げている(Photo06)。特にリアルタイム系のアプリケーションではこれが顕著で、より広帯域かつ大容量のメモリが必要とされている事は今更説明の必要はないだろう(Photo07)。ご存知の通りIntelはすでにXeon E5でDDR4をサポートしており、今後Xeon E3やXeon E7もDDR4に移行する。ということは、膨大なサーバーの入れ替え需要、あるいは新規需要が発生するが、この際にはメモリの入れ替えが伴う事になる。後で数字が出てくるが、サーバのDRAM容量は今後3年で2倍になり、また2017年には80%、2018年には100%のサーバがDDR4に移行を果たすと見込んでいる。当然サーバ向けのDDR4 DIMMの需要があるということは、DDR4 Chipsetへの需要も同じだけあるという事になる。RAMBUSは、ここに一定の商機があると見込んだ訳だ。

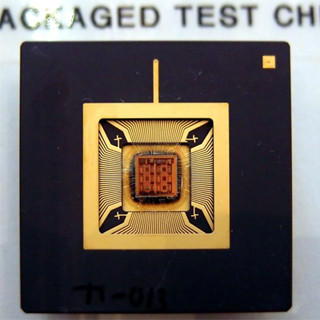

さて次の話は、「だからといって何故チップを作り始めたのか」である。これに関する直接的な答えは無いのだが、基本的に同社はMemory I/Fに関して非常に多くの知見と大量の特許を抱えており、これを利用して現在市場に出ているものより優れたChipsetを提供できる、としている(Photo08)。実際同社の「RB26」は、すでにDDR4-2666に対応できる性能で、設計上はDDR4-2933までサポートしており、さらに周波数ベースの電力最適化を実装しているという(Photo09)。この「周波数ベースの最適化」とは何か? と後でTsern博士に確認したところ、幾つかあるものの、そのうちの1つは例えば非常に粒度の細かいClock Gatingを行っているとか。なので動作周波数が下がるほど消費電力を下げられるとの事だった。

さて、話を戻すと同社はこれまでIPの提供をするのがメインのビジネスであり、それは現在も変わっていない。そこで、チップを提供するにあたっては、既存のIPを購入してくれるクライアントと市場でぶつからない様に細心の注意を払った、とする。具体的に言えばメモリ分野では、Samsung/SK Hynix/Micronという3大メモリベンダはいずれもRAMBUSの大手クライアントであり、IPライセンスを含む広範な契約をすでに結んでいる。なので、こうしたメモリベンダが現在行っているビジネスには絶対に手を出さない様にしている。そのためメモリチップを自身で作ったりしないのは言うまでもなく、DIMMモジュールの製造販売についても手を出さないとしている。「サーバ向けのDIMMモジュールの9割は、メモリチップベンダ自身が提供している。だから、ここでDIMMモジュールを製造すると、彼らのビジネスとぶつかる事になる。なので、DIMMモジュールは作らない」という訳だ。逆にDDR4のChipsetは? というと「DDR4のChipsetは(メモリメーカーに比べると)もっと小さいビジネスであり、しかも我々のライセンシーは存在しない。だからここで我々がチップを販売しても、ライセンシーと競合することは無い」とした。

そこで意地悪く「ではもし、他のメーカーがRAMBUSからIPを購入してDDR4のChipset Businessに参入したいと考えた場合、RAMBUSはIPをライセンスするのか?」と聞いたところ「今のところそういう事は特に考えていない。もしそうした状況になったら熟慮する必要があるだろう」という返事が返ってきた。要するになぜRAMBUSがDDR4 Chipsetを自身で製造するか、といえば

- DDR4 Chipset向けのIPを社内で開発完了し(もしくは既存のIPの組み合わせでDDR4 Chipsetが構築できることが証明され)、それなりに良い製品になるという判断があった

- にも関わらず、そのIPに対してどこのChipsetメーカーも興味を示さなかった

- そのため、自身で製造販売することにした

というあたりが正直なところではないか、と思う。つまりすでにDDR4 Chipsetを作る可能性がありそうなメーカーには当たった上で、同社のIPを使いたいというメーカーが無い事が確認されたので、自社での製造に踏み切った、ということではないかと思う。

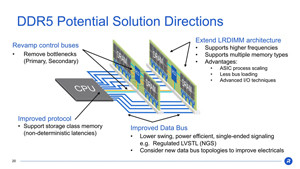

もう1つ深読みすると、今回の製品投入はDDR4の世代だけでなく、さらにその先まで見据えての可能性がある。Photo10はやはりIDFのSponsor Sessionからのものだが、DDR4世代の次として、DDR5に関する検討がすでにJEDECなどで開始されている。ここでDDR5世代に求められる事として(Sponsor Sessionの中で)RAMBUSは

- 6.4Gbps以上までのスケーラビリティ

- 2DIMM per Channelの実現。さらにDRAMとSCM(Storage Class Memory)の混在の実現

- 現在のマザーボードインフラを最大限に活用でき、低リスクで移行できること

- DDR4と比べてプラットフォーム/システムコストの上昇を最小限に抑える

- CPUの変更の最小化(特にピン数)

- DDR4からの移行をスムーズに行えること

- レイテンシと消費電力を最小限に抑えること

- DDP(Dual Die Package)と3DS(3D Stacking)の両方をサポートすること

の8項目を挙げており、これを実現するための方法としてDDR5 LRDIMMを発展させる方法が潜在的に可能性があることを示している(Photo10)。実際同社は2013年に6.4Gbpsで動作するDDR5のプロトタイプを完成させ、2013年のISSCCで発表している。このDDR5世代で例えば製品あるいはIPのどちらを販売する形になるとしても、そのためにはDDR4世代での実績があったほうが好ましく、この実績作りという意味でも今回のChipsetは意味が大きいと思われる。

さて、それではどうやって販売するか? であるが、基本的にはこれまで書いたとおりサーバ向けのDIMMモジュールのほとんは、3大メモリベンダが販売する形になるので、RAMBUSとしては各メモリベンダにChipsetを納入する形になる。これにあたり、RAMBUSはまずIntelと密接な関係を取り、共同でChipsetの開発や検証を行ったとする。これは「現在(x86)サーバの98%はIntel製なので、まずIntelと共同で行う事が非常に重要になる」(Tsern博士)との事。もっとも他のプラットフォームを無視している訳ではなく、「もちろんARMとかPOWERもこの後対応してゆくことになるが、まず最初はIntelから、ということだ」(Naraghi氏)という話である。IntelでのValidationが済んでいる、というのはある意味メモリベンダにとっても有り難い話であって、というのはメモリベンダの販売するモジュールもほとんどはIntelのサーバ向けだから、これは検証のコストを削減するという意味でも大きい。実際名前は未公開ながら、あるメーカーからChipsetの開発を強く望まれたという事情もあるそうで、なので(出荷数量がどの程度になるか)はともかく、食い込むことそのものはめどが立っているらしい。先のSK HynixのLabel InformationにはまだRAMBUSの名前は無いが「確かに現状ではまだ名前が無いが、まもなくここにRAMBUSが加わる事を期待している」(Naraghi氏)という話だった。