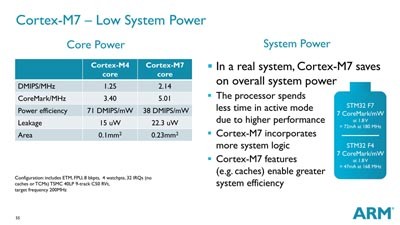

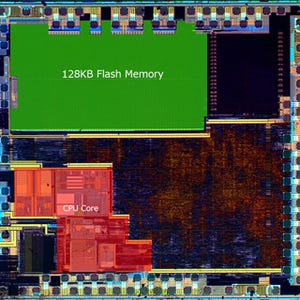

最後がダイエリアと消費電力の話である(Photo20)。TSMCの40nm Gプロセスを使った場合、Cortex-M4だとCPUコアのエリアサイズが0.1平方mmなのに対し、Cortex-M7では0.23平方mmなので、2倍以上になる。実際には、Cortex-M4はTCMとかキャッシュがなくてもそれなりに動作するのに対し、Cortex-M7ではキャッシュやTCMは半ば必須となるので、これを加味すると0.3平方mmを超えて0.4平方mm近くなるかもしれない。なので、90nmプロセスあたりでこれを製造するのはコストにかなりのインパクトになるだろう。ただし40nmあるいは28nmでこれを製造すると、周辺回路を含めても1~2平方mmで納まるから、既存のMCUの価格帯で十分製造できることになる。その意味では、Cortex-M7のターゲットは40nm以下のプロセスで主戦場は28nmということになりそうだ。

もうひとつの問題は消費電力で、Power EfficiencyとLeakageのどちらもCortex-M7はCortex-M4より悪化している。まぁこれだけ複雑なパイプライン構成と周辺回路であれば、悪化して当然ではあるのだが、それでもその分性能が高いから、右にあるように同じ性能/消費電力比(7 CoreMark/mW)を実現するのに必要な動作周波数はむしろ下がるため、トータルとしてはCortex-M4よりも高効率である、という話だった。

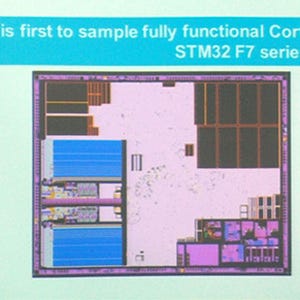

ただこれに関しては既存のSTM32 F7はSTM32 F4と同じく90nmプロセスでの製造だから、Flashのアクセス速度が(Flash Acceleratorの助けを借りるとは言え)一応動作速度に追いついており、パイプラインにWaitが入らない。ところが40/28nmとなると絶対的に追いつかないから、当然Waitが入りまくることになり、その分性能が悪化する事が予測される。これをどう考えるか尋ねた所「だからこそL1 Cacheがあるわけで、ここでうまくCacheにHitするようにすることでWaitを最小限に抑え、高効率に実行できる」という返事が返ってきた。確かにロジックとしてはその通りであるが、今度はプログラムをいかに効率的に書くかという問題が発生する事になる。それは単にプログラムの書き方だけではなく、コンパイラの生成するコード自身も問題になってくる訳だ。もちろんMCUなんだからアセンブラで書けという意見もあるかもしれないが、Cortex-M7自身のポジショニングがかなりハイパフォーマンスな、アプリケーションプロセッサに近い位置づけにされているから、流石に高級言語を使うなという議論は非現実的であろう。そんな訳で、単にハードウェアだけではなく、ソフトウェア側の最適化次第で性能とか消費電力が結構変わってきそうな、ややピーキーなMCUになったということは言えそうだ。

もう1つInterruptまわりで。通常MCUでは、ISRは特定アドレスに置かれていて、Interruptが入るとRegisterのStackなどが終わったらそのアドレスにJump(というかVector Tableにそのアドレスが入っている)という形をとる事になり、これはCortex-M7でも同じである。ところが、Memory SubsystemはCortex-M7の場合直接には触れず、間にI-Cacheが介在するケースが一般的だ。Phto19に戻ると、Interruptが入るとFront-endのVector Fetchが動作してそのアドレスの命令を実行し始めることになるが、ここでI-Cacheが必ずHitするとは限らない。で、もしCache-Missした場合、先の11~12cycleというLatencyを守れるとはちょっと考えにくい。なので、例えばISRの先頭ブロックは常にI-Cacheに入れておくといった工夫が無いとLatencyがかなり大きくなりそうなのだが、そうした仕組みは今のところハードウェア的にもソフトウェア的にもCortex-M7には入ってなさそうである。一応Cortex-M7のProcessor Technical Reference Manualによれば、ISRはAXIやAHBの先に置く事も可能らしいが、実際問題としてはTCMの中にISRを常駐させておく使い方が一番現実的に思える。これそのものはコンパイラというかリンカへの指定だけで済むだろうが、色々と気をつけてやる必要があること自体は間違いなさそうだ。

ということで、Cortex-M7の詳細についてのレポートをお届けした。実は最近、Corte-M4コアが高性能向けというよりはやや省電力向けにシフトしつつある気がする。先鞭をつけたのはEnergy Micro(現Silicon Labs)が2013年に発表したEFM32 Wonder Geckoで、Cortex-M4Fコアながら動作周波数は48MHzに抑え、その代わり稼動時で225μA/MHz、Shutoff Modeでは20nA@3Vまで消費電力を落としている。今年1月にはAmbiq MicroがやはりCortex-M4Fコアを24MHz駆動とし、その代わり動作時が30μA/MHz、Sleep時に100nAまで省電力を落としたApollo MCUを発表、4月にはTIがやはりCortex-M4Fをベースとした省電力MCUとしてMSP432を発表しているなど、省電力向けの新製品投入が目立っている。もちろんこの背景には、Cortex-M4をベースとした高性能/普及帯製品はほぼ各社とも一段落しているので、低消費電力向けにシフトしているという事情もあるのだが、この先のプロセス微細化を考えるとCortex-M4ベースのままではそれほど性能も上げにくい。なので、今後はCortex-M7コアベースのMCUが各社のハイエンド品向けに投入され、Cortex-M4は今のCortex-M3が占めているメインストリーム向けを置き換えてゆく形になりそうだ。