|

Cypress Semiconductorは4月24日(米国時間)、ARM Cortex-M0を搭載したプログラマブルSoCアーキテクチャ「PSoC 4」の第1弾製品として「PSoC 4100ファミリ」および「PSoC 4200ファミリ」の出荷を開始したことを発表した。

従来の8051プロセッサを搭載したPSoC 3とARM Cortex-M3を搭載したPSoC 5の間のナンバリングが施された同シリーズは、M8Cプロセッサを搭載したPSoC 1の後継に位置づけられており、「アナログへの回帰を図ったシリーズ」(同社)とする。そのため開発の際に最も重視されたのが、プロセッサの性能でもデジタルロジックの数でもなく、アナログをプログラマブルに扱えるかどうかという点にあることを強調する。

性能としては、4100ファミリが24MHz駆動で、フラッシュの容量は8KB~32KB、LPコンパレータが2個、オペアンプ数が1もしくは2、そしてプログラマブルなデジタルブロック(Universal Digital Block:UDB)が0となっているほか、12ビットの逐次比較型(SAR)A/Dコンバータ(ADC)が1つ搭載されている。一方の4200ファミリは48MHz駆動で、フラッシュ容量は16KB~32KBで、128KB品は現在開発が進められているとのこと。その他のLPコンパレータ、オペアンプ、ADCなどの部分は同じながら、UDBが2~4搭載されており、プログラマブルロジックとしてデジタル部分の機能を自由に構築することが可能となっているほか、従来のCPUファンクションをUDBへ移行することも可能で、これにより自立した高信頼性回路の構築なども可能となった。

また2ファミリとも、同社が提供する静電容量タッチセンシング技術「CapSense」を搭載しており、タッチセンサと接続して利用することも可能だ。

さらに、新たに低消費電力に向けた電力モードとして、従来の「Active」「Sleep」「Hibernate」に加え、「Deep Sleep」および「Stop」を追加。StopモードはWAKEUPOピンとXRES(リセット)のみ起こした状態にすることで、消費電流20nAを実現することが可能だという。

同社では4100ファミリはエントリレベルなどの製品に、4200ファミリはミドルレンジクラスの製品への適用といった使い分けを想定しており、「ピンコンパチブルであり、開発もPSoC Creatorを用いることで、PSoC 3/5を含めて共通して行うことが可能であるため、用途に応じて容易に設計変更を行うことが可能」とする。

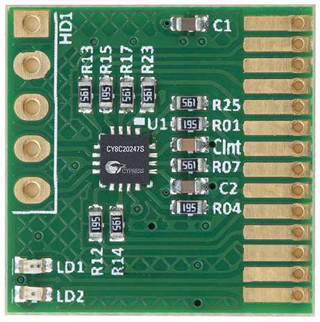

なお、価格についての詳細は明らかにされていないが、型番によっては1ドルで提供可能なものもあるとするほか、Arduinoプラットフォームとフォームファクタ互換の開発プラットフォーム「PSoC 4 Pioneer Kit(CY8CKIT-042)」も25ドルで提供が行われている。また、PSoC 4シリーズとしては上位互換となる4400ファミリ、ならびに4600ファミリの開発が現在進められており、こちらはUDBの数が増えるほか、新たなアナログアルゴリズムとなる「UAB(Universal Analog Block)」も搭載され、アナログ機能の強化が図られる予定だとしている。