Xilinxは、プログラマブルかつ柔軟性とコスト効率に優れた3G+/4G無線基地局の構築に不可欠な新しい3つのコネクティビティIPコアを発表した。

今回提供されたIPコアは「Serial RapidIO Gen 2 v1.2 Endpoint LogiCORE IP」、「JESD204 v1.1 LogiCORE IP」、および「CPRI v4.1 LogiCORE IP」で、いずれもコネクティビティ規格をサポートしているため、開発者は、より大きなシステム容量を備える新しい無線装置の構築時に直面する設計課題への取り組みに集中できるようになると同社では説明している。

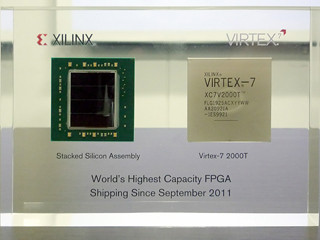

Serial RapidIO Gen 2 v1.2 Endpoint LogiCORE IPは、RapidIO Trade AssociationのRapidIO Gen 2.2仕様に対応した設計がなされており、×1/2/4レーン幅で最大6.25GラインレートをサポートするGen2.2 ソフトIPコアである。柔軟性が高く、最適化されたSerial RapidI物理層コアおよびロジック(I/O)とトランスポート層コアで構成されており、同社のFPGA「7シリーズ」や「Virtex-6」をサポートしている。

またこのコアには、コンフィギュレーション可能なバッファ デザイン、リファレンスクロックモジュール、リセットモジュールが含まれているほか、ファブリック コンフィギュレーションのリファレンスデザインも用意されているため、特定アプリケーションに合わせたファンクションブロックの選択における自由度が改善される。さらに、FPGA/CPU/DSPマルチプロセッサファーム間のデータ帯域幅が2倍になり、増加するデータスループットに対応できるよう無線基地局などのシステムに複雑な演算機能や信号処理機能を実装することが可能となるという。

2つ目のCPRI v4.1 LogiCORE IPは、CPRI(Common Public Radio Interface)規格 v4.2に対応しており、無線制御部(REC:Radio Equipment Controllers)またはベースバンド/チャネルカードと1つまたは複数の無線部(RE:Radio Equipment、無線通信カード)間を接続するためのコア。CPRIプロトコルは、基地局の分離とクラウドベースのRAN(Radio Access Network)というコンセプトに基づき、基地局とRRHを分離した構成にすることが可能である。

そして、JESD204B v.1.1 LogiCORE IPは、データコンバータへのワイドパラレルインタフェースを1/2/4レーンの高速シリアルインタフェースリンクに置き換えることで、I/O制約における問題を解消し、低コストでシンプルなPCBレイアウトを実現することができるようになるというもの。シリアルデータインタフェースおよびデータコンバータとロジックデバイス間のリンクプロトコルを定義する「Joint Electron Devices Engineering Council (JEDEC) JESD204B」規格に対応して設計されたソフトIPコアで、7シリーズでサポートされる。これを用いることで、DACデバイスとインタフェースするJESD204Bトランスミッタもしくは、ADCデバイスとインタフェースするJESD204Bレシーバとして活用することが可能になるという。

なお、いずれのIPも同社のデザインツールスイートの最新版「ISE Design Suite 13.3」にて提供される。