Alteraは10月13日(米国時間)、組み込みシステムにおけるプログラマブル・ロジックとプロセッサの融合の加速を目指す「エンベデッド・イニシアチブ」を発表した。

|

|

AlteraのVice President,Product&Corporate MarketingであるVince Hu氏 |

同イニシアチブの策定の背景について、同社Vice President,Product&Corporate MarketingのVince Hu氏は、「組込機器に搭載されるソフトウェアの要求性能が年々高まってきている。そうした要求に対するハードウェア側の答えとしては、マルチコアやハードウェア・アクセラレーションといった並列処理の方向性が打ち出されている。しかし、例えばアクセラレータを活用しようと思っても、機器を開発する前段階において、どの機能がどの程度のアクセラレータを活用するのかを見極めるのは難しい。そこで、FPGAを用いて柔軟にCPU+アクセラレータを活用しようというのが、今回のイニシアチブの考え方」と説明する。

|

|

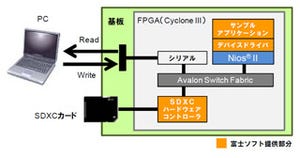

市場のトレンドはマルチコア化とアクセラレータの活用による処理性能の向上。FPGAをアクセラレータとして活用するというのはHPC分野でも使われて来た話で、FPGAの中にCPUコアを搭載することで、CPUのマルチコア化とアクセラレータとしての役割を1チップで行わせようというのが今回のイニシアチブの大筋 |

現在、多くの組込機器がFPGAを活用し始めており、「組み込みエンジニアの42%はFPGAを用いてアプリケーションの開発を行った経験がある」(Hu氏)とのことで、「我々のカスタマの多くも、(Alteraの提供するソフトコアである)NIOS IIを用いて開発した経験があり、そうした意味ではCPUとFPGAの両方を扱ったことがあるといえる。FPGAにCPUを搭載して活用することで、機器の小型化や部品点数の削減などが可能となる」(同)とし、すでにそうした方向性(CPU+FPGAという考え方)は世の中に多くでており、IntelもAtom E600toFPGAを1チップに搭載した「Stellarton」をIDF Fall 2010にて発表している。

|

|

|

左がIntelの提示するムーアの法則とのテクノロジーギャップをどうやって埋めるかの図。Stellartonでは、FPGAをアクセラレータとして活用することで性能向上を図ろうとしている。右がIBMがFPGAを暗号ソフトウェア「Common Cryptographic Architecture(CCA)」などの処理に活用したSystem Z10の例 |

|

「CPU+FPGAという動きは、今後数年間で確実に採用件数が増えることが見込まれる。しかし、それを容易に実現するためには、1つのFPGAのデザインフローでCPU、FPGAともに扱えるようにする必要がある」(同)とのことで、今回のイニシアチブには以下の3つの要素が含まれている。

- 開発ツールの整備(ハードウェアの視点からのツール)

- (Intel、MIPS、ARMなどとの)アライアンスの確立

- エコシステムの開発

上記のHu氏の発言はこのエコシステムとツールにかかるもので、2010年第4四半期に提供される同社のFPGAデザインソフトウェア「Quartus II」のバージョン10.1に、従来のシステムレベル統合ツール「SOPC Builder」に変わる新たな統合ツール「Qsys(キューシス)」と、FPGA用共通ライブラリが提供される予定とのこと。なお、SOPC BuilderとQsysは「バックヤードコンパチブルのため、現在の資産も有効活用できることもあり、しばらくSOPC Builderのサポートも行うが、将来的にはQsysへと移行を行ってもらうこととなる」(同)とのこと。

なお、Qsysはパイプラインのレジスタ処理などの部分におけるレイテンシのパラメータ調整を自動で行ったり、CPUとFPGAの接続なども自動で行うことが可能。さらに「SOPC Builderはポイントtoポイントの接続のみで、そこが性能のボトルネックとなっていた。Qsysではリング構造やスター構造など、最適なトポロジを自動で判断する」(同)といったことを行うことで、最大2倍の性能向上が可能となったという。

また、アライアンスの確立については、すでにIntelが発表しているStellartonも含め、パートナープログラムの拡充の一環が進められており、ARMとMIPS Technologiesという2つのプロセッサコアとのエコシステム構築が行われる。ちなみに、プロセッサコアの拡充についてHu氏は「7年前、FPGAにとってトランシーバ機能はマイナーだった。しかし、現在ではメジャーな機能として活用されるようになった。プロセッサについても、今はまだマイナーな機能という扱いだが、今後はメジャーな機能となると予測しており、より多くのカスタマが活用することを確信している」との力強い答えが返ってきた。

具体的には、ARMとはハード化したARM Cortex-A9ベースのサブシステムを28nmプロセス採用FPGAに統合した製品を2011年に提供するというもの。マルチコアも対象に含まれており、「Cortex-A9を選んだ理由は、現在すでに流通しているARMコアとして最も高性能で、多くのカスタマが活用に動いている。我々はCPU+FPGAを進める上で、カスタマが慣れていないコアよりも、ニーズにあった性能で、かつ慣れているコアを選択する必要があった。そうした意味ではCortex-A9がベストな選択だった」(同)とする。

一方のMIPSに対する対応だが、こちらはソフトコア「MP32」としてソフトコアプロセッサの製品群拡大が行われ、2011年初頭に発表される予定。すでにソフトコアとしてはNIOS IIがあるが、この住み分けについては「NIOS IIはとにかく低コストながらプロセッサを活用したい場合。例えばマイコンなどにも活用できる。MIPSについては、逆にパフォーマンスが欲しい領域での活用を見込んでいる」(同)との住み分けが想定されている。また、ソフトコアのため、「アーキテクチャが大きく変わらなければ、どのプロセスでもサポートできると考えており、従来のプロセスにも適用はできる」(同)とのことで、発表できるような案件があれば、随時、そうした前世代のプロセスでの採用例なども発表していきたいという。

ARM Cortex-A9はハード化されているが、MIPSはソフトコア。このほか、ColdFireやARM Cortex-M1などもソフトコアで対応しており、こうしたプロセッサのラインアップの拡充についてHu氏は「カスタマがターゲットニーズに応じて使い分けてもらえればと思い拡充している。パワーとかサイズ、カスタマが何を求めているのかを常にリサーチし、それに対応するべく、幅広い領域をサポートするのが我々の務め」としており、x86についてはIntelが推し進めるが、それについてもサポートは行っていくとしており、自社がIntelからAtomコアのライセンスを受け、FPGAにそれを入れて提供ということは予定していないという。

なお、Alteraでは今回のイニシアチブを第一歩として、「CPU+FPGAをより簡単に扱えるようにしていく。そのためのサポートと多くのオプションを用意していく。それはAlteraだけの取り組みだけでなく、IntelがAlteraを採用したように、外部での活用も含めてだ」(同)としており、今後も組込分野に向けCPU+FPGAの活用を目指して取り組みを進めていくとした。