東芝は、16nmプロセス世代以降の低消費電力かつ高性能なLSIの実現に向け、トランジスタ構造の有力候補として検討されている立体構造トランジスタ「ナノワイヤトランジスタ」において、寄生抵抗を低減し、オン電流を従来比75%向上させることが可能となる新たな技術を開発したことを明らかにした。同技術の詳細は、2010年6月15~17日に米国ハワイ州で開催される半導体デバイスに関する国際会議「VLSI技術シンポジウム(2010 Symposium on VLSI Technology)」にて17日(現地時間)に発表される予定。

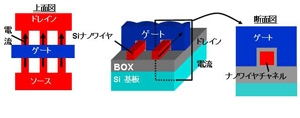

ナノワイヤトランジスタは、トランジスタのチャネル部がナノメートル級のワイヤ形状のSiからなるトランジスタ(MOSFET)で、細線状のチャネルをゲートが取り囲むためにゲートによる制御性能が向上し、短チャネル効果によるオフ時のリーク電流の抑制が可能だ。しかしその一方で、ゲート電極とソース-ドレイン電極との間の絶縁層(ゲート側壁)下に存在する細線状のソース・ドレイン領域において、寄生抵抗が増大し、オン電流が低下するという課題があった。

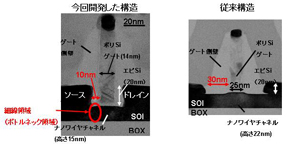

今回、東芝が考案した構造は、この側壁下の細線領域を短くして寄生抵抗増加を抑制しようというもの。ゲート側壁加工の最適化によってゲート側壁を10nmまで薄くし、細線領域を従来比1/3まで縮小した。また、ソース-ドレイン電極上のみにSiをエピタキシャル成長させて体積を増加させる手法を取り入れることで、ソース-ドレイン電極の低抵抗化を実現した。

開発した手法を用いたn型トランジスタのオン電流を測定すると、従来の30nm厚のゲート側壁に比べて40%向上が確認されたほか、チャネル部分のSi層の結晶方位を従来の<110>方向からウェハ面上で45度回転した<100>方向にすると、n型トランジスタのオン電流が25%向上することも確認されたという。

これにより、オフ電流100nA/μmのもとでオン電流は従来比75%向上の1mA/μmが達成され、シリコンナノワイヤトランジスタのオン電流において世界トップレベルの電流量が実現されたこととなる。

なお、同社では今後、今回開発した技術を生かした高性能で低消費電力なLSIの研究開発を行っていくとしている。