条件実行命令と逆数近似命令

また、SIMD拡張を有効に利用できるようにするための命令として、浮動小数点Compare(FCMP)命令とFCMP命令の結果を使用するFSELMOV命令などがHPC-ACEで新設されている。

FCMP命令は、rs1とrs2レジスタの内容を比較し、指定した条件(EqualとかGreaterThanなど)と一致した場合は、rdレジスタにall-1、一致しない場合はall-0を書き込む。新設のFSELMOV命令はrs3の値が"1"の場合はrs1、"0"の場合はrs2を選択してrdに書き込む。条件成立の場合の処理結果をrs1に入れ、条件不成立の場合の処理結果をrs2に入れて、この命令を使用すれば条件分岐命令が不要となり、パイプライン処理の乱れを防ぐことができる。さらに、B側とE側で条件の成立/不成立が異なる場合でも並列に処理が可能であり、SIMDの利用効率を高めることができる。

また、rs2の値が"1"の場合だけにストアを実行するSTFDR命令が新設されており、結果のメモリへの格納の場合は、この命令を使えば良い。

そして、もう1つのSIMD拡張を有効に利用する新設命令として、逆数近似命令と平方根逆数近似命令がある。一般的には、除算はハードウェアのループで処理されるので、乗算と違ってパイプライン的に毎サイクル新しい演算を行うことが出来ず、スループットが低いという問題がある。これに対して、適当な初期値からNewton法やGoldschmidt法を使ってソフトウェアのループで精度を改善していく方法では、ハードウェアとしては通常の加算や乗算を行うだけであり、毎サイクル新しいデータをパイプライン的に処理できるので、SIMD機構を有効に利用して除算のスループットを上げることができる。

このために設けられたのが8ビット精度の逆数や平方根逆数を与える命令である。Newton法などでは1回のループで有効桁数を倍増できるので、8ビット精度から開始すると、3回のループで倍精度浮動小数点数に必要な精度で結果が得られる。そしてSPARC64 VIII fxの場合はSIMD拡張を利用すると各コアで4つの逆数計算を並列して実行することができる。

なお、科学技術計算では距離の逆数に比例する力の計算というのは良く出現するパターンであり、x、y、zの距離の二乗和を計算し、それの平方根の逆数を計算するという処理が行われる。この後半の平方根の逆数が3回のループで4個計算できるのは、非常に効率的である。

ハードウェアバリア機構

SPARC64 VIII fxは8個のプロセッサコアを1チップに集積しており、

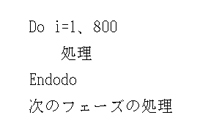

のようなケースでは、プロセッサ0はi=1、100、プロセッサ1はi=101、200、プロセッサ3はi=201、300というように分担して処理すれば効率が良い。しかし、各プロセッサでの処理に掛かる時間が同一でない場合は、次のフェーズの処理に入る前に、全プロセッサの処理の完了を待ち合わせる必要がある。このとき、完了を待ち合わせるための処理時間が本来のi=1、100までの処理時間に比べて無視できない比率になってくると8コアでの並列処理の効果が低下してしまう。

この待ち合わせ処理を高速化するため、SPARC64 VIII fxではハードウェアバリアという機構を装備している。このハードウェアバリア機構は12個のバリアブレードを持ち、そのうちの4個のバリアブレードは各8ビットのBarrier Status(BST)ビットとBarrier Maskを持っている。これらの8ビットの各ビットはCPUコアに固定的に対応しており、マスクが"1"となっているコアのBSTビットがすべて"0"、あるいは"1"に揃うと、そのバリアブレードのLast Barrier Status(LBSY)ビットをその値にセットする。そして、LBSYビットの状態が変化すると、スリープ状態のスレッドを実行状態に変更するという機能を持っている。

つまり、前述のように8個のプロセッサコアで分担して処理を行い、すべてのコアでの処理が終了するのを待って、次のフェーズの処理を開始するというような場合、このバリアブレードの自分のBSTビットをまず"0"にして処理を開始し、各コアは自分の処理を終了するとBSTビットを"1"に変更してスリープする。そうすると、最後に処理を終了したコアがBSTビットを"1"にセットした時点で、バリアブレードのLBSYビットが"1"になり、全コアが同時に実行状態に戻って次のフェーズの処理を開始する。

なお、次のフェーズでは、処理を完了したコアはBSTビットに"0"を書き込むようにすれば、BSTビットの初期化を行う必要はない。

このような処理の待ち合わせをメモリ上の変数を使って行うと、各コアが状態を記憶する同一のバイトに書き込みや読み出しアクセスを行うため、コア間のキャシュラインの移動が発生したり、他のプロセッサの完了をスピンループでチェックすることによるオーバヘッドが生じるが、このハードウェアバリア機構を用いると、同期のオーバヘッドが少なく、小さな処理単位でプロセッサ並列の処理を行ってもコア並列の効果が出る。

また、残りの8個のバリアブレードは 1ビットのBSTビットだけを持つバリアブレードであり、これらは2つのスレッド間の待ち合わせのために使用される。