SXAR前置命令でレジスタ指定を拡張

しかし、SPARCの命令長は32ビットであるので、ここに3つ、あるいは4つのレジスタ指定を収めようとすると、それぞれのレジスタ指定に使えるビット数は5ビット程度が限界である。このため、SPARC(やその他のRISCプロセッサでも)の浮動小数点レジスタ数は32個になっている。

例外として、IntelのItaniumは256個のレジスタを持っているが、そのために、命令長は41ビットと長い命令を使用することになっている。また、CELLのSPEは128個のレジスタを持ち、32ビット長の命令の中に7ビットのレジスタ指定を4つ詰め込んでいるが、SPEは汎用プロセッサではないので、必要な命令の種類数が少ないのでこれが可能になっている。

今回、SPARC64 VIII fxで採られたレジスタ数の拡張方法はユニークなものである。256個のレジスタを指定するには8ビットが必要であり、元々の命令に含まれる5ビットでは3ビット不足する。これを、XARレジスタというレジスタ番号指定フィールドを拡張するレジスタを設けて補っている。

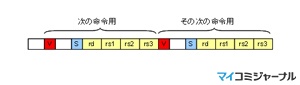

次の図に示すように、XARレジスタは、それに続く2つの命令に対して、FMA命令で必要となる3つのソースオペランドとリザルトのレジスタ指定の拡張分と、そのデータがValidであるかどうかを示すVビットと、その命令をBasicとExtendedの両方で並列に実行するSIMD動作を指定するSビットを持っている。

そして、XARレジスタに値を書き込むsxar1とsxar2という命令を設け、sxar1命令の場合は、次の命令はsxa1命令で指定した次の命令用のレジスタ拡張ビットを使い、 sxar2命令はそれに続く2つの命令でレジスタ拡張ビットを使う。また、sxar命令が前置されていない命令では拡張ビットを使わず、従来のSPARC64プロセッサと同じ動作となる。つまり、sxar命令は、ある意味では、x86のPrefix命令のように次に続く命令の動作を修飾するように動作する。

しかし、これでは1~2回の演算やロードストア命令に対して、レジスタの番号を指定するためのsxar命令が必要になってしまい、実行命令数が増えてしまう。

実際にどのように実装されているのかは情報が無く不明であるが、プロセッサ内部の処理ではレジスタ指定は常に8ビットで扱い、命令デコードの時点で、このsxar命令の3ビットのレジスタ番号拡張と後続の演算命令の5ビットの指定を繋いで8ビットのレジスタ番号に変換してしまえば、sxar命令により命令数が増えるオーバヘッドは命令フェッチからデコードまでであり、演算を実行する時点では命令数は増えない。したがって、このような実装方法を採ることにより、 sxar命令によって実行命令数が増加することによる性能低下を無視できるレベルに抑えることは可能であると思われる。