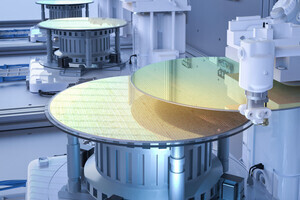

2020年6月27日~29日に中国上海で開催された半導体製造装置材料の展示会である「SEMICON China 2020」の関連行事として、「中国国際半導体技術大会(China Semiconductor Technology International Conference:CSTIC2020)」がリアルとバーチャルな会議の組み合わせで開催された。

基調講演4件を含むオープニングセッションは6月29日午前に上海でリアルな講演会として開催され、その他の一般講演は7月17日までオンライン・オンデマンド講演としてバーチャル開催された。

基調講演のテーマはムーアの法則に沿った微細化の課題

Applied Materials(AMAT)、TSMC、ASML、Intelによる4件の基調講演はいずれも「ムーアの法則」に沿った半導体デバイスの超微細化に関するテーマで、いずれもムーアの法則による微細化の限界とそれを打破するためのプロセス・材料や実装技術の工夫に関する内容だった。中国勢のデバイスの微細化に対する並々ならぬ関心の高さがうかがえ、この分野の世界中の叡智を招待して、超微細化技術を熱心に習得しようとしているように見受けられた。

材料やプロセスの工夫でさらに微細化 - AMAT

世界最大の半導体製造装置メーカーである米Applied Materials(AMAT)のCorporate VP(前職はIntel研究開発部門)のSanjay Natarajan氏は「ムーアの法則をさらに前進させるために」と題して講演した。

同氏によると、微細化のスピードは、2015年前後からスローダウンしており、ロジックデバイスの第1メタル(M1)層のピッチおよびDRAMのSTI(シャロートレンチアイソレーション)ピッチの微細化速度は遅くなってきている。

過去40年に渡り、IC搭載のトランジスタ数は、「ムーアの法則」にしたがい、2年に2倍の割合で継続的に増えてきた。しかし、最近のデータでは、5年に2倍とトランジスタ増加速度はスローダウンしており、ムーアの法則に陰りが見えてきたとNatarajan氏は指摘した。

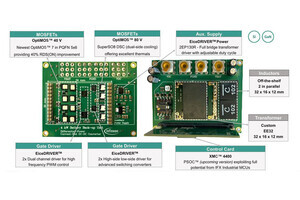

これを打破して、ムーアの法則をさらに継続させるために、システムアーキテクチャの変更、3D化を含むデバイス構造の変更、新しい3D実装技術の開発に加えて、周期律表の中から最適の元素を探して従来の材料と置き替えたり、プロセスを工夫する手法が必要だとして、自社の装置での実例を上げながら説明した。例えば、前後のプロセスの同時最適化、前後のプロセスを統合した装置、計測機能の製造装置への統合による前後の装置へのフィードバックやフィードフォワード、プロセスフローの改良などである。最近特に注目されているPPAC(パフォーマンス向上、パワー低減、エリア低減、コスト低減)を改善するためには、従来のような2次元の微細化だけではなく、これらの工夫が必要であると同氏は指摘した。

チップレットで歩留まり向上しムーアの法則を延命 - TSMC

TSMCの研究開発担当VPのDoug Yu氏は、「次の大きなフロンティア:チップレットとその先」と題して講演した。

同氏も「ムーアの法則」から話を始めた。1987年(TSMC創業年)以来、トランジスは連続して微細化し、その寸法はほぼ1/1000に縮小した。10nm以降の微細化でつまずいたIntelと異なり、微細化が順調に進んでいるTSMCの立場でYu氏は、現在に至るまでムーアの法則は健在であることを強調した。

しかし、ムーアの法則にしたがいICに搭載されるトランジスタ数が増加するとチップサイズが大きくなり、歩留まりが急激に低下してしまい、結果としてコストが急騰してしまう。

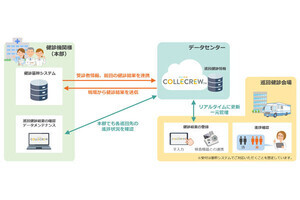

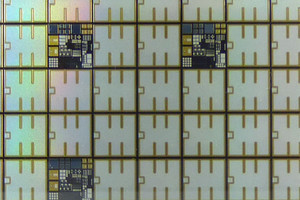

例えば、平均欠陥密度が0.15個/cm2の場合、図示したように、チップ面積が40mm2のICの歩留まりは75%だが、120mm2と3倍になると歩留まりは40%に低下し、10倍の400mm2になると歩留まりはわずか5%へと急激に低下してしまう。

-

チップサイズをパラメータとした平均欠陥密度と歩留まりの関係。チップサイズが大きいほど歩留まりは急速に低下するので、チュップレットを用いて個々のチップサイズを小さくすることで歩留まり向上を図る方向にある

この問題を解決する手段として、「チップレット」と呼ばれるICのパーツ(一部分だけ切り出したもの)を活用する手法が注目されている。従来のチップを構成する微細なパーツをレゴのように組み合わせてプロセッサをつくるという発想で、その活用にIntelやAMDといった主要メーカーが動き始めた。標準規格の策定を模索する動きもあるなか、「ムーアの法則」による半導体の進化のスピードを維持する切り札になることが期待されている。