本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

MJアーキテクチャプロセサのタイミング図とブロックダイヤグラム

以上で定義した命令を実行するMJアーキテクチャプロセサのタイミング図を次に示す。

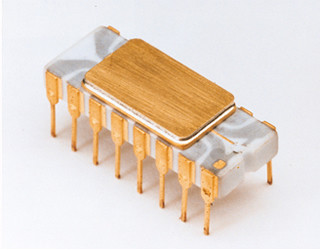

A1~A3サイクルでROMに12ビットの命令アドレスを送り、M1、M2サイクルで8ビットの命令を読み出すのは4004と同じである。そして、RAM、あるいはI/Oをアクセスしない場合は、X1~X3サイクルで命令の実行を行う点も4004と変わらない。

一方、RAMやI/Oをアクセスする場合は、X2~X4の3サイクルで12ビットのアドレスをRAMに送る。そして、X5サイクルに、ストアの場合はCPUからRAMにデータを送り、ロードの場合はRAMからのデータを受け取る。

RAMにアドレスを送るのに3サイクルを必要としているが、RAMを選択する命令が不要になり、かつ、I/OもメモリマップドI/OとしてRAMと同じ手順でアクセスするようにしたので、4004では必要であったI/O命令やSRC命令の場合の特殊な制御が不要になり、すっきりとしたタイミング図となっている。

次の図にMJアーキテクチャ 4ビットプロセサのブロックダイヤグラムを示す。

このブロックダイヤグラムは4004のブロックダイヤをベースに、インデックスレジスタとROM、RAMをアクセスするためのCM Logicを削除し、PCにくっついていた3本のスタックレジスタを4本のインデックスレジスタに変更したものであり、全体として4004より簡単な構造となっている。

MJアーキテクチャで追加された機能をサポートするため、PCとIXレジスタの+1を行うインクレメンタからのキャリーを記憶するIXCYフラグ(1ビットレジスタ)を追加し、この値を条件分岐の判定を行うCCブロックに接続している。そして、コントロールからの線は、IXCYフラグをクリアするためのものである。

また、MJアーキテクチャでは、通常の演算命令は4004と同じくX3サイクルで実行を終わるが、RAMやI/Oをアクセスする命令はX6サイクルまで必要となるので、このタイミング発生を切り替えるため、コントロールからタイミング回路に制御線が追加されている。

そして、ブロックダイヤグラム上では見えないが、命令の定義が異なるので、命令デコーダやコントロールは、MJアーキテクチャに合わせて新たに設計する必要がある。