そして求解対象の問題に応じて4種類の計算原理を使い分けられるアニーリング計算機構造として、「Metamorphic Annealer(Amorphica)」が設計された。Amorphicaは全結合型のイジングモデルに対し、スピンを逐次的にも並列にも更新可能であり、安定性と高速性のバランスを保ったアニーリング処理を実現できたという。

さらにAmorphicaのもう1つの大きな特長に、スケールアップが可能な点がある。全結合型のイジングモデルを分散アニーリングする場合、その過程で頻繁に同期処理が必要となり、その際の通信コストが大きな課題となる。今回の研究では、スピン更新情報を転送する過程に圧縮符号化を導入することで同課題が解決された(Amorphicaは復号回路を搭載)。

-

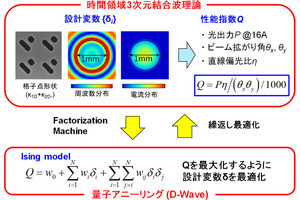

Amorphicaアーキテクチャの核となるフリップスピン選択回路。循環シフタで入力配列要素を乱数分だけ左に移動(あふれた要素は右端に移動)させ、マスカでマスク配列との要素積が計算される。最後に、プライオリティエンコーダを用いて、最も左に位置する値1の要素のインデックスが抜き出される(出所:JSTプレスリリースPDF)

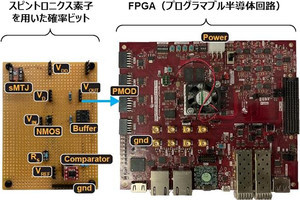

その後、TSMCの40nmプロセスを用いてAmorphicaが設計・試作された。チップサイズは3mm×3mmで、単チップでは512スピンに対するアニーリング処理を4レプリカ並列で実行可能。その際の消費電力は最大でも500mWに満たないとする。また、同チップはFPGAを介して最大4チップを接続可能であり、最大2048スピンに対するアニーリング処理を実現するとしている。

実際に同チップを4個接続したアニーリングシステムを用いて、4種類の「最大カット問題」を解いた結果、対GPU比で最大58倍の高速化が達成され、約3万倍の電力効率で同品質の解が得られることが確認された。

研究チームは、Amorphicaを小型IoT機器などに組み込むことで、低電力ながら高速に解を探し出す汎用組み合わせ最適化ソルバとしての活躍が見込まれるとした。

また同研究チームは今後、Amorphicaチップに基づくアニーリングシステムの早期実用化を目指すという。その中で、今回の研究で扱われた「組み合わせ最適化問題の性質と最適な計算原理の相関調査」をより広域な実応用問題へと拡張し、多様な組み合わせ最適化問題に適応できるようにすることが求められるとした。