書き換え時間の短縮技術も開発

また、読み出しだけが高速化しても書き換えに時間がかかってしまってはボトルネックとなってしまうため、その高速化も必要とされた。すでにIEDM 2021において、低消費電力かつ高速な書き換えを実現する書き換え電圧印加時間の短縮技術として、同時書き換えビット数の最適化技術を報告しているが、今回の研究では、さらなる高速化に向け、動作モード間の遷移待ち時間の短縮に向け、内部電圧のセットアップ待ちの時間を短縮する回路構成・制御手法を新たに採用したとする。

従来は書き込み電圧を全ビットの書き込みが可能なほど高く設定していたが、その発生には昇圧回路(チャージポンプ回路)が必要であり、その電力供給制限から、128ビットや256ビットといったように書き込みターゲット(単位)を分割して、書き込み電圧を印加していた。これを今回の研究では、ごく少量、0.01%程度のビット書き込みミスを許容することで、電圧を下げることが可能である、ということを利用して、最初にマイコンのI/O用電源からの降圧により発生した低い書き換え電圧を書き換え単位の全ビットに一括印加し、そこでミスが生じた少数のビットに対し、昇圧回路を使って高い電圧を印加することでカバーするという手法を採用。これにより、大部分の書き換え単位については1回の書き換え電圧印加で書き換えが終了することとなり、結果として電圧印加時間の75%削減に成功したとするほか、残った書き換え単位の部分についても50%の削減が可能になったという。

さらに、書き換え電圧の立ち上げ前に書き換え対象のアドレスをMRAMマクロに入力することで、書き換え用の高電圧を印加する書き込みドライバやワード線ドライバなどへの電圧がかかることを絞り込み、一部分だけ書き込み電圧を印加させるようにすることで、書き換え電圧発生回路出力の寄生負荷を低減し、書き換え電圧印加モードへの遷移時間を30%短縮することにも成功したとする。

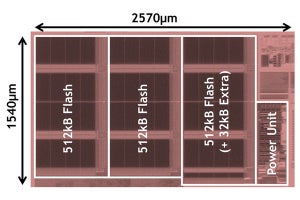

22nm混載STT-MRAMプロセスで試作チップを製造

実際に、これらの回路技術を盛り込んだ22nm混載STT-MRAMプロセスにて32Mビットの試作チップをTSMCのシャトルサービスを用いて製造。接合温度150℃においても100MHzを超す読み出し動作を可能とする5.9nsのランダムリードアクセス時間を達成したほか、接合温度-40℃~+150℃において5.8MB/sの書き込み速度を達成したという。

ちなみに22nm混載STT-MRAMプロセスとなったのは、利用可能なTEGであったためで、技術的にはその先のプロセスとなる16nm混載STT-MRAMプロセスなどでも適用できるとするほか、TSMC以外のファブでも適用できるプロセスであるという。

将来的には製品への適用に道筋

研究チームでは要素回路技術的には読み込みならびに書き込みともに基本動作の重要部分については今回までの研究でクリアでき、回路の要素技術的に見れば、製品に適用できるレベルに達したとの見方を示している。ただし、製品に適用する場合には、信頼性評価などを行っていく必要があることもあり、実際にマイコン製品として今回の技術などが活用される時期は未定だという。

また、150℃での動作が確認されたことで、車載マイコンへの適用なども期待されることから、今後はそうした車載グレードに対応するための信頼性の向上や、さらなる低消費電力化、高性能化の追求などを進めていきたいとしている。

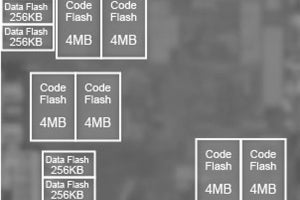

なお、今回の混載STT-MRAMプロセスが実用化されたとしても、ルネサスとしては混載フラッシュプロセスは170℃対応といったメリットや、読み込み速度が混載STT-MRAMに比べてまだ速い場合などもあり、カスタマのニーズにマッチするものを勘案して最適な製品の提供を行っていければとしている。