産業技術総合研究所(産総研)は5月31日、SiC耐電圧1.2kVクラスのSiC縦型MOSFETと、SiC CMOSで構成された駆動回路を1チップに集積した「SiCモノリシックパワーIC」のスイッチング動作を実証することに成功したと発表した。

同成果は、産総研 先進パワーエレクトロニクス研究センター パワーデバイスチームの岡本光央主任研究員、同・原田信介研究チーム長、同・パワー回路集積チームの八尾惇研究員、同・佐藤弘研究チーム長らの研究チームによるもの。詳細は、6月3日までオンラインで開催中の「The 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD)」において、6月1日のオーラルセッションで発表されたという。

SiCは、従来のパワー半導体材料であるシリコンに比べて優れた物性を持つことから次世代パワー半導体材料として縦型MOSFETなどの製品化が進められている。現在、SiCパワー半導体とSiC CMOSを1チップ上に集積するモノリシックパワーICの開発が世界中で進められているが、その製造の難しさから、成果報告はそれほど多くないという。その理由としては、高電圧でも壊れないように設計されたSiC CMOS駆動回路は出力電流が小さいため、SiC縦型MOSFETをスイッチング動作させることが困難であるという点が挙げられるという。

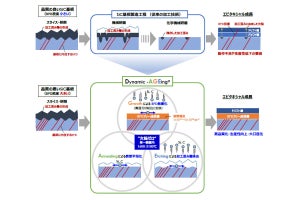

これまで産総研は、SiCパワーデバイスの量産に向けた技術開発を進めてきており、独自構造のSiCパワーMOSFETとして第1世代の「IE-MOSFET」、第2世代の「IE-UMOSFET」を開発してきたほか、SiC CMOSに関する研究も進めており、製造プロセスの要素技術開発や特性評価、ならびにSiCパワーデバイスを用いたスイッチング技術についての研究開発などを進めてきたという。研究チームは今回、これらの研究成果を結集させ、1チップ上にIE-UMOSFETとSiC CMOSを集積したSiCモノリシックパワーICの開発を試みたという。

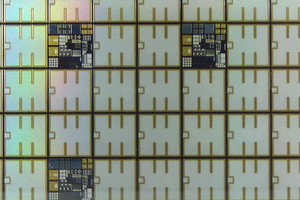

その結果、縦型MOSFETとCMOS駆動回路を1チップ上に集積することに成功。配線信号長を従来比で短くできるようになり、小型軽量化を実現できるとともに、寄生インダクタンスの低減を図ることもできたという。

具体的には、縦型MOSFET領域とCMOS駆動回路領域の2つの領域から構成されるが、IE-UMOSFETと共通のp型層の上にCMOS駆動回路を形成することで、「p型MOSFET出力の電流増大」および「耐電圧」の両立を可能としたという。

なお、実際の動作試験では、ドレイン電圧600V、ドレイン電流10Aでスイッチング動作が可能であることが確認されたという。

この成果を踏まえ研究チームでは今後、SiC CMOS駆動回路の出力電流をさらに増大させ、SiCモノリシックパワーICの高速スイッチングを目指すとしているほか、さらにセンサやロジック回路なども集積させるなどの高機能化を進めることによって利便性も高めていきたいとしている。